# 24bit, 192KHz 双通道, 差分输出数模转换电路

# 产品简述

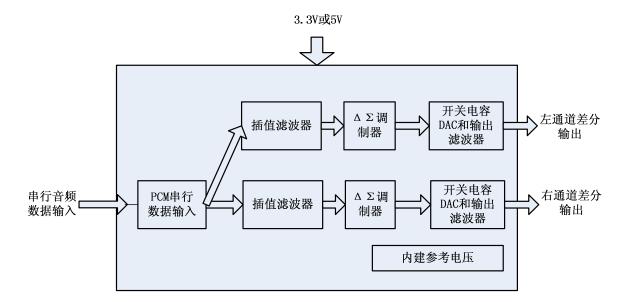

MS5281D是一款立体声数模转换芯片,内含插值滤波器、multi bit数模转换器、差分输出模拟滤波器。MS5281D支持大部分的音频数据格式。MS5281D基于一个带线性模拟低通滤波器的四阶multi-bitΔ-Σ调制器,而且本芯片可以通过检测信号频率和主时钟频率,在2KHz 和200KHz 之间自动调节采样率。

MS5281D可以工作在3.3V和5V下。这些特性使它成为DVD播放解码器、数字通信设备等无线设备的理想选择。

MS5281D 采用 DFN12 封装。

## 主要特点

- Muti-bit∆Σ调制器

- 24bit D/A 转换器

- 自动检测最大到 192KHz 的信号频率

- 110dB 动态范围

- 0.003% 总谐波失真

- 低时钟抖动敏感度

- 3.3V 或 5V 工作电压

- 线性滤波输出

- 封装形式: DFN12

### 应用

- 数字通讯设备

- 汽车音响系统

- DVD 音频系统

#### 产品规格分类

| ı | / 111177 UH 74 2 | <u> </u> |       |

|---|------------------|----------|-------|

|   | 产品               | 封装形式     | 丝印名称  |

|   | MS5281D          | DFN12    | 5281D |

DFN12

## 内部框图

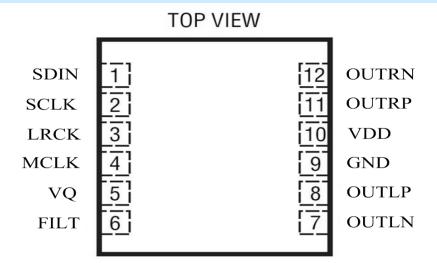

## 管脚排列图

# 管脚描述

| 管脚编号 | 管脚名称  | 管脚属性 | 管脚描述       |

|------|-------|------|------------|

| 1    | SDIN  |      | 串行音频数据输入端  |

| 2    | SCLK  | I    | 外部串行时钟输入端  |

| 3    | LRCK  |      | 左/右时钟端口    |

| 4    | MCLK  | I    | 主时钟端口      |

| 5    | vq    | 10   | 直流电压       |

| 6    | FILT  | 10   | 正的参考电压     |

| 7    | OUTLN | 0    | 模拟左通道负输出端口 |

| 8    | OUTLP | 0    | 模拟左通道正输出端口 |

| 9    | GND   | -    | 地          |

| 10   | VDD   | -    | 模拟电源       |

| 11   | OUTRP | 0    | 模拟右通道正输出端口 |

| 12   | OUTRN | 0    | 模拟右通道负输出端口 |

## 极限参数

## 绝对最大额定值

注意: 绝对最大额定值表示不被破坏的限界,不保证实际工作状态

| 参数     | 符号               | 额定值                     | 单位         | 注 |

|--------|------------------|-------------------------|------------|---|

| 供电电压   | VDD              | -0.3~7                  | V          |   |

| 输入管脚电流 | I <sub>in</sub>  | -10~+10                 | uA         | _ |

| 数字输入电压 | V <sub>IND</sub> | -0.3∼VDD+0.3            | V          |   |

| 工作温度   | T <sub>OP</sub>  | -55~125                 | $^{\circ}$ | _ |

| 存储温度   | $T_{stg}$        | <b>−65</b> ~ <b>150</b> | $^{\circ}$ | 1 |

### 工作电源电压范围

|        |                |     | 参数范围 |     |            |   |

|--------|----------------|-----|------|-----|------------|---|

| 参数     | 符号             | 最小  | 标准   | 最大  | 单位         | 注 |

| 电源电压范围 | VDD            | 3.0 |      | 5.5 | V          | 1 |

| 温度范围   | T <sub>A</sub> | -40 |      | +85 | $^{\circ}$ | 1 |

# 电气参数

## DAC 模拟特性

(TA = 25°C,满幅输出正弦信号, 997Hz, Fs=48/96/192kHz; RL = 3kΩ, CL = 10pF,测试带宽 10 Hz 至 20kHz。)

| ·            |                     |            |         |         |         |     |

|--------------|---------------------|------------|---------|---------|---------|-----|

|              |                     | 3.3V       |         | 单位      |         |     |

|              | 参数<br>              |            |         |         |         |     |

| 动态性能         |                     |            |         |         |         |     |

| 动态范围         | 24 bit              | A-weighted | 100     | 102     |         | dB  |

| 总谐波失真        |                     |            |         |         |         |     |

|              | 24 bit              | OdB        | 0.003   |         |         | %   |

|              |                     | -60dB      | 0.1     | 0.3     |         | %   |

| 隔离度          |                     |            |         |         |         |     |

| 通道隔离度(1KHz)  |                     |            | 95      | 100     |         | dB  |

| DAC 精度       | _                   |            |         |         |         |     |

| 通道间增益匹配误差    |                     |            |         | 0.1     | 0.2     | dB  |

| 模拟输出         |                     |            |         |         |         |     |

|              |                     |            | 0.63*VD | 0.66*VD | 0.69*VD |     |

| 满幅度输出电压      |                     |            | D       | D       | D       | Vpp |

| 直流电压         | V <sub>Q</sub>      |            |         | 0.5•VDD |         | VDC |

| AOUT 端最大直流电流 | I <sub>OUTmax</sub> |            |         | 3.3     |         | mA  |

| VQ 端最大电流     | $I_{Qmax}$          |            |         | 1       |         | mA  |

| 最大阻性负载       | $R_L$               |            |         | 1       |         | kΩ  |

| 最大容性负载       | C <sub>L</sub>      |            |         | 1000    |         | pF  |

| 输出阻抗         | Z <sub>OUT</sub>    |            |         | 110     |         | Ω   |

## 滤波特性

| 参数              | dr          | 符号  | <b>具</b> 小店 | 曲刑店    | 最大值    |    |

|-----------------|-------------|-----|-------------|--------|--------|----|

|                 | Χ           | 打亏  | 最小值         | 典型值    | 取入阻    | 单位 |

| Single-Speed 模式 |             |     | 1           | T      | 1      |    |

| 通频带             | 至 -0.1dB 拐点 |     |             |        | 0.35   | Fs |

| <b>世</b> 奶市     | 至 -3dB 拐点   |     |             |        | 0.4992 | Fs |

| 40Hz 到 15KHz 自  | り频率响应       |     | -0.07       |        | +0.55  | dB |

| 衰减带             | i<br>I      |     | 0.54        |        |        | Fs |

| 衰减幅             | 度           |     | 55          |        |        | dB |

| 群延时             | ţ           | Tgd |             | 10/fs  |        | S  |

| Double-Speed 模式 |             |     |             |        |        |    |

| 77 LT - 11-     | 至 -0.1dB 拐点 |     | 0           |        | 0.22   | Fs |

| 通频带             | 至 -3dB 拐点   |     | 0           |        | 0.501  | Fs |

| 40Hz 到 15KHz 自  | り频率响应       |     | -0.02       |        | +0.2   | dB |

| 衰减带             | Ť           |     | 0.54        |        |        | Fs |

| 衰减幅             | 度           |     | 55          |        |        | dB |

| 延时              |             | Tgd |             | 5/Fs   |        | S  |

| Quad-Speed 模式   |             |     |             |        |        |    |

|                 | 至 -0.1dB 拐点 |     | 0           |        | 0.11   | Fs |

| 通频带             | 至 -3dB 拐点   |     | 0           |        | 0.469  | Fs |

| 40Hz 到 15KHz 自  | り频率响应       |     | -0.01       |        | +0.1   | dB |

| 衰减带             |             |     | 0.54        |        |        | Fs |

| 衰减幅             | 度           |     | 55          |        |        | dB |

| 延时              |             | Tgd |             | 2.5/Fs |        | S  |

# 数字输入特性

| 参数    | 符号              | 最小值     | 典型值  | 最大值 | 单位 |

|-------|-----------------|---------|------|-----|----|

| 输入高电平 | V <sub>IH</sub> | VDD-0.6 |      |     | V  |

| 输入低电平 | $V_{IL}$        |         |      | 0.6 | V  |

| 输入漏电流 | l <sub>in</sub> |         | 0.02 |     | uA |

| 输入电容  |                 |         | 3    | 8   | pF |

# 功耗参数

| 参数   |      |                |     | 3.3V |     |    |

|------|------|----------------|-----|------|-----|----|

|      |      |                | 最小值 | 典型值  | 最大值 | 单位 |

|      | 工作状态 | I <sub>A</sub> |     | 16   | 25  | mA |

| 工作电流 | 关闭状态 | I <sub>A</sub> |     | 100  |     | uA |

|      | 1KHz | PSRR           |     | 70   |     | dB |

| 电源抑制 | 60Hz | PSRR           |     | 50   |     | dB |

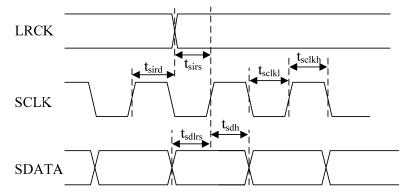

# 开关特性(串行接口)

| 参数                     |                 | 符号     | 最小值 | 典型值 | 最大值 | 单位  |

|------------------------|-----------------|--------|-----|-----|-----|-----|

| MCLK                   | 频率              |        | 2   |     | 50  | MHz |

| MCLK 1                 | 占空比             |        | 45  |     | 55  | %   |

|                        | 256x,384x,1024x | Fs     | 8   |     | 50  | kHz |

|                        | 256x,384x       |        | 84  |     | 134 | kHz |

| /A > IV                | 512x,768x       |        | 42  |     | 67  | kHz |

| 输入采样率                  | 1152x           |        | 30  |     | 34  | kHz |

| (MCLK/LRCK)            | 128x,192x       |        | 50  |     | 100 | kHz |

|                        | 64x,96x         |        | 100 |     | 200 | kHz |

|                        | 128x,192x       |        | 168 |     | 200 | kHz |

| LRCK -                 | 古空比             |        | 45  | 50  | 55  | %   |

| SCLK 刖                 | 永宽低             | tsclkl | 20  |     |     | ns  |

| SCLK 刖                 | 永宽高             | tsclkh | 20  |     |     | ns  |

| SCLK 占空比               |                 |        | 45  | 50  | 55  | %   |

| SCLK 上升沿到 LRCK 边沿的延迟   |                 | tslrd  | 20  |     |     | ns  |

| SCLK 上升沿到 LRCK 边沿的建立时间 |                 | tslrs  | 20  |     |     | ns  |

| SDIN 有效到 SCLK 上升沿的建立时间 |                 | tsdlrs | 20  |     |     | ns  |

| SCLK 上升沿到 S            | DIN 的保持时间       | tsdh   | 20  |     |     | ns  |

外部串口输入时序:

### 功能描述

MS5281D 接受标准的音频采样频率,包括在QSM 模式下的48、44.1、32kHz,在DSM 模式下的96、88.2、64kHz,在SSM 模式下的192、176.4、128kHz。音频数据通过串行输入数据端输入(SDIN)。左/右通道时钟(LRCK)决定当前输入数据的通道。串行时钟是音频数据进入输入数据缓存的时钟。

#### 主时钟

MCLK/LRCK 的比值必须是整数,见下表。LRCK 的频率等于每个通道输入数据的频率Fs。MCLK 与LRCK 的比值和速度模式是在初始化时通过计算在一个LRCK 周期内MCLK 的周期数以及MCLK 的值来决定的。内置的除法器会产生合适的时钟。下表 列出了一些音频采样频率,以及相应的MCLK 和LRCK频率。请注意这里虽然没有相位的要求,但是LRCK 和MCLK 必须同步。

| 在总及主虽然仅有相应的女外, |       |           |         |         |         |        |        |  |

|----------------|-------|-----------|---------|---------|---------|--------|--------|--|

|                | LRCK  | MCLK(MHz) |         |         |         |        |        |  |

| mode           | (kHz) | 128x      | 256x    | 384x    | 512x    | 768x   | 1024x  |  |

|                | 32    | -         | 8.192   | 12.288  | 16.384  | 24.576 | 32.768 |  |

| QSM            | 44.1  | 5.6448    | 11.2896 | 16.9344 | 22.5792 | 33.868 | 45.158 |  |

|                | 48    | 6.144     | 12.288  | 18.432  | 24.576  | 36.864 | 49.152 |  |

|                | 64    | 8.192     | 16.384  | 24.576  | 32.768  | 49.152 | -      |  |

| DSM            | 88.2  | 11.2896   | 22.5792 | 33.868  | 45.1584 | -      | -      |  |

|                | 96    | 12.288    | 24.576  | 36.864  | 49.152  | -      | -      |  |

|                | 128   | 24.576    | 32.768  | 49.152  | -       | -      | -      |  |

| SSM            | 176.4 | 22.5792   | 45.1584 | -       | -       | -      | -      |  |

|                | 192   | 24.576    | 49.152  | -       | -       | -      | -      |  |

表: 时钟频率

#### 串行输入时钟

MS5281D 数据格式(I<sup>2</sup>S)

I<sup>2</sup>S, 最高可到24bit数据数据在SCLK的上升沿有效

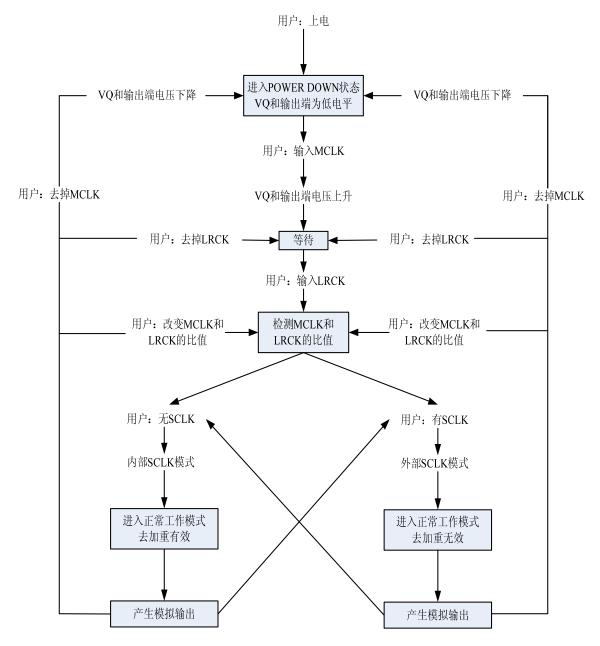

### 初始化和Power-Down

当系统初始上电后就进入 power-down 状态,此时插值滤波器和 ΔΣ 调制器复位,内部参考电压、数模转换器、开关电容滤波器、低通滤波器被关闭,直到系统检测到 MCLK 和 LRCK 时钟。一旦 MCLK 和 LRCK 被检测到,系统就开始计算 MCLK 和 LRCK 的比值,然后给内部参考电压上电,最后才给数模转换器、开关电容滤波器上电,同时输出端输出静态电压 VQ。

#### 输出瞬态控制

MS5281D 采用Pop-guard 技术来减小上电和下电时的瞬态响应。

#### 上电

输出端的直流电平就由 VQ 端提供,当系统初始上电时,VQ 端为低电平。当MCLK 检测到后,VQ 端产生正常的直流电压。当VQ 端接10uF 电容需400ms的启动时间。

#### 下电

为了防止在下电时输出端产生瞬态脉冲,VQ端外接10uF电容,以保证MCLK在下电前停止,在这段时间内VQ端和输出端逐渐下降到GND。当需要改变时钟频率或采样频率时,最好在LRCK保持10个周期的低电平信号。在时钟变换的过程中,DAC将保持低电平输出。初始化和power down流程如下图所示:

初始化和Power-Down 的顺序图

#### 接地与电源去耦合

MS5281D 地与电源的连接必须非常注意以达到理想的性能。为了得到最好的性能,去耦合与滤波电容必须尽可能的靠近芯片。

# 典型应用图 R5 | C1 | C1 | -5V | C2 | AN R6 OUTR\_N OUTR\_P 11 120pF OUTL N 12K BISA 12K C12 10uF R channel L channel R channel GND C8 0.1 OUTR\_N R212K OUTR\_P OP07 R8 47K GND C9 0.1 VQ FILT C4 430P OUTL\_P OUTL\_N GND MS5281 L channel SDIN SCLK LRCK OUTR\_N R\_out\_-R\_out\_+ VDD 6 FILT OUTL P L\_out\_+ 330 L out -GND MS5281 10n 10n 10n 10n GND

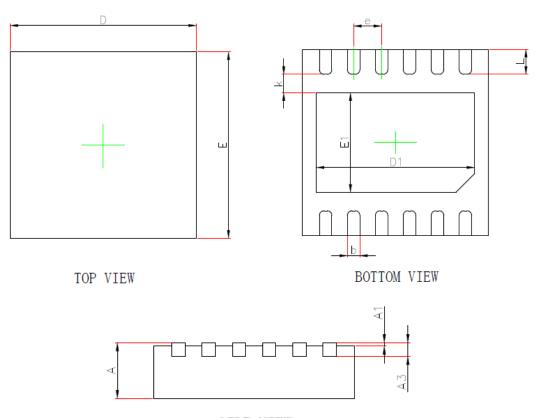

## 封装外形图

### DFN12:

DFNWB3 $\times$ 3-12L(P0.45T0.75/0.85) PACKAGE OUTLINE DIMENSIONS

SIDE VIEW

| Symbol | Dimensions I | n Millimeters | Dimension   | s In Inches |

|--------|--------------|---------------|-------------|-------------|

| Symbol | Min.         | Max.          | Min.        | Max.        |

| Α      | 0.700/0.800  | 0.800/0.900   | 0.028/0.031 | 0.031/0.035 |

| A1     | 0.000        | 0.050         | 0.000       | 0.002       |

| A3     | 0.203        | REF.          | 0.008       | REF.        |

| D      | D 2.924      |               | 0.115       | 0.121       |

| E      | 2.924        | 3.076         | 0.115       | 0.121       |

| D1     | 2.450        | 2.650         | 0.096       | 0.104       |

| E1     | 1.500        | 1.700         | 0.059       | 0.067       |

| k      | 0.200        | OMIN.         | 0.008       | BMIN.       |

| b      | 0.150        | 0.250         | 0.006       | 0.010       |

| е      | 0.450        | TYP.          | 0.018       | TYP.        |

| L      | 0.324        | 0.476         | 0.013       | 0.019       |

## 印章与包装规范

### 一、印章内容介绍

### 1. 印章内容介绍

5281D: 产品型号

生产批号:

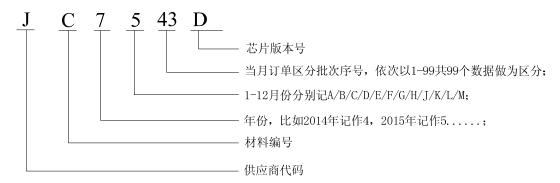

范例: JC7543D

## 2. 印章规范要求

采用激光打印,整体居中且采用 Arial 字体。

### 3. 包装说明

| 型号      | 封装形式  | 只/盘  | 盘/盒 | 只/盒  | 盒/箱 | 只/箱   |

|---------|-------|------|-----|------|-----|-------|

| MS5281D | DFN12 | 5000 | 1   | 5000 | 8   | 40000 |

MOS电路操作注意事项:

静电在很多地方都会产生,采取下面的预防措施,可以有效防止MOS电路由于受静电 放电的影响而引起的损坏:

- 1、操作人员要通过防静电腕带接地。

- 2、设备外壳必须接地。

- 3、装配过程中使用的工具必须接地。

- 4、必须采用导体包装或抗静电材料包装或运输。

杭州市滨江区伟业路1号 高新软件园 9号楼 701室

http:// www.relmon.com