## 802.3af Compliant PD interface with High Efficiency Flyback Converter

Preliminary Specifications Subject to Change without Notice

## DESCRIPTION

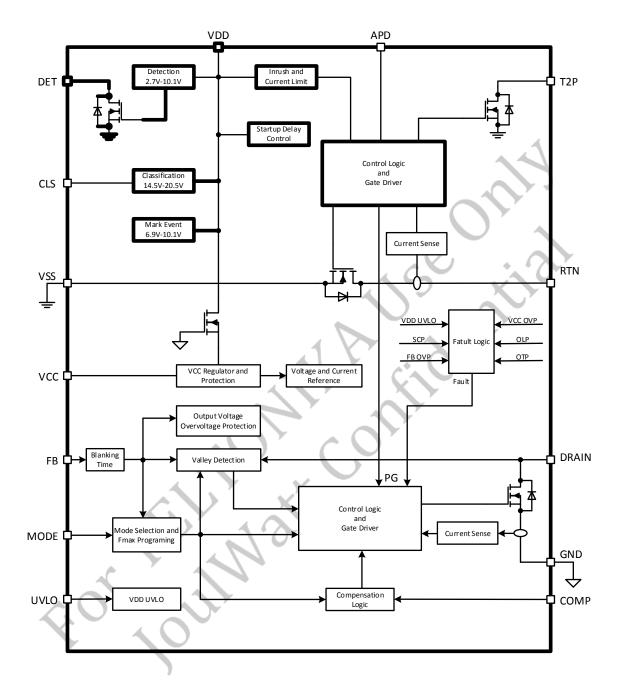

The JW®H7232 is an integrate IEEE 802.3af PoE complaint Powered Device (PD), it includes PD interface and high efficiency flyback controller.

The JWH7232 has all the functions of IEEE 802.3af, including detection, classification, power up inrush and operation current limit as well as a Hot-swap MOSFET.

The DCDC converter uses primary-side regulation without opto-coupler feedback, simplifying the system design. It also supports secondary-side feedback design.

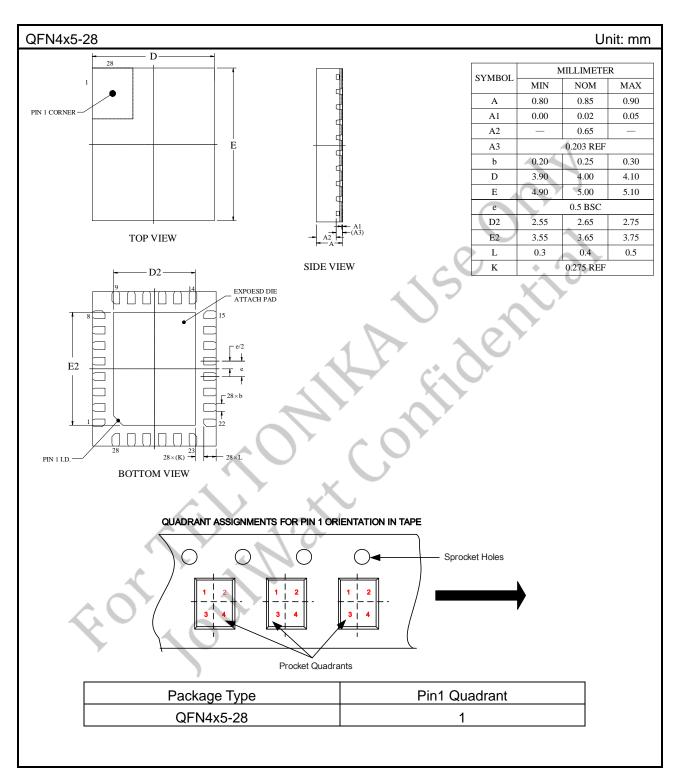

The JWH7232 is available in a space-saving 28-pin QFN (4mm × 5mm) package.

Company's Logo is Protected, "JW" and "JOULWATT" are Registered

Trademarks of JoulWatt technology Inc.

## **FEATURES**

- Compatible with IEEE 802.3af specifications

- Integrate 100V PD hot-swap MOSFET

- Auxiliary adaptor oring power Supply

- Support multiple topology design Primary-side regulated flyback Secondary-side regulated flyback

- Output diode compensation in PSR mode

- Up to 500kHz adjustable switching frequency

- Hiccup protection for OLP, OVP and thermal shutdown

- EMI reduction with frequency dithering

- Available in 28-pin QFN 4mm x 5mm-28 package

## **APPLICATIONS**

- IEEE 802.3af-compliant devices

- Security camera

- WLAN access points

- IoT devices

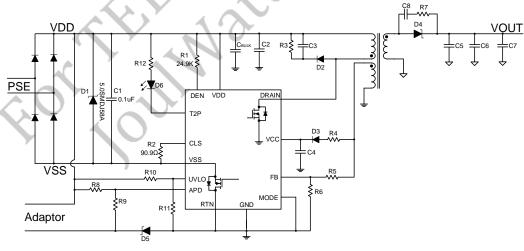

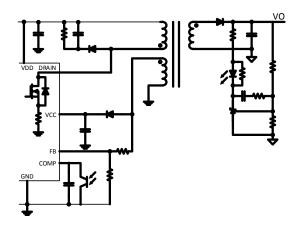

## TYPICAL APPLICATION

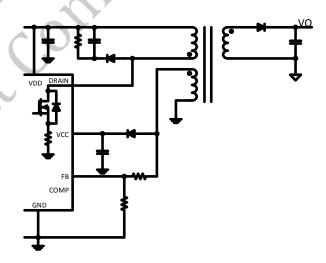

**PSR** typical application

Unauthorized Photocopy and Duplication Prohibited.

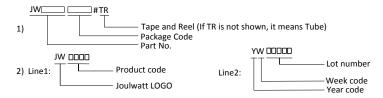

## ORDER INFORMATION

| DEVICE <sup>1)</sup> | PACKAGE         | TOP MARKING <sup>2)</sup> | ENVIRONMENTAL <sup>3)</sup> |

|----------------------|-----------------|---------------------------|-----------------------------|

| IW/H7222OENI I#TD    | QFN4*5*0.85-28  | JWH7232                   | Groon                       |

| JWH7232QFNU#TR       | QFIV4 5 0.65-26 | YW□□□□                    | Green                       |

#### Notes:

3) All Joulwatt products are packaged with Pb-free and Halogen-free materials and compliant to RoHS standards.

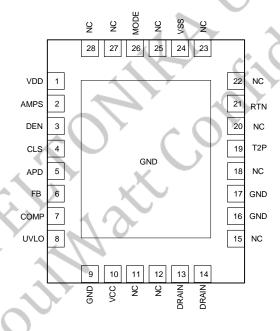

## **PIN CONFIGURATION**

## **ABSOLUTE MAXIMUM RATING1**)

| Pins Voltage Respects to VSS:                             |                         |

|-----------------------------------------------------------|-------------------------|

| VDD, RTN, DEN, T2P, APD, GND                              | 0.3V to 100V            |

| AMPS                                                      | 0.3V to 100V            |

| CLS                                                       | 0.3V to +6.5V           |

| Pins Voltage Respects to GND:                             |                         |

| VDD                                                       | ,-0.3V to 100V          |

| DRAIN                                                     |                         |

| FB, COMP                                                  | 0.7V to 100V            |

| VCC                                                       | 0.3V to 20V             |

| MODE, UVLO                                                | 0.3V to +6.5V           |

| Pins Voltage Respects to VDD:                             |                         |

| APD                                                       | 6.5V to +0.3V           |

| Pins Current:                                             | 7 50 7.0                |

| T2P Sinking Current                                       | 10mA                    |

| VCC Sinking Current                                       | 1.5mA                   |

| APD Sinking Current                                       | 5mA                     |

| FB Sinking Current  Junction Temperature <sup>2) 3)</sup> | ±2mA                    |

| Junction Temperature <sup>2) 3)</sup>                     | 150°C                   |

| Lead Temperature (Soldering, 10 sec)  Storage Temperature | 260°C                   |

| Storage Temperature                                       | 65°C to +150°C          |

| RECOMMENDED OPERATING CONDIT                              |                         |

| Supply Voltage VDD                                        | 0V to 57V               |

| Switching Voltage V <sub>DRAIN</sub>                      | 0.5V to 150V            |

| Maximum T2P Sinking Current                               | 5mA                     |

| Maximum VCC Sinking Current                               |                         |

| Maximum APD Sinking Current                               |                         |

| Maximum FB Sinking Current                                |                         |

| Maximum Switching Frequency                               | 500kHz                  |

| Maximum Switching Current Limit                           |                         |

| Operating Junction Temperature                            | 40°C to 125°C           |

| ELECTROSTATIC DISCHARGE RATING                            | <b>3</b>                |

| Human Body Model (HBM)                                    | ±2kV                    |

| Charged Device Model (CDM)                                |                         |

| THERMAL PERFORMANCE <sup>4)</sup>                         | <b>0</b> JA <b>0</b> JC |

| QFN4x5-28                                                 | 40°C/W 9°C/W            |

|                                                           |                         |

#### Note:

1) Exceeding these ratings may damage the device. These stress ratings do not imply function operation of the device at any other conditions beyond those indicated under RECOMMENDED OPERATING CONDITIONS.

- 2) The JWH7232 includes thermal protection that is intended to protect the device in overload conditions. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

VDD, CLS, DET, APD, T2P and RTN voltages are referred to VSS, and all other pin voltages are referred to GND, GND and RTN are shorted together. The  $\bullet$  denotes the specifications which apply over the full operating temperature range(-40°C to 125°C), otherwise specifications are at  $T_A$ =25 °C. VDD-VSS=48V, VSS=0V, and  $R_{DEN}$ =24.9K $\Omega$ ,  $R_{CLS}$ =41.2 $\Omega$ , unless otherwise noted.

| Item                                        | Symbol                | Condition                                                                                   |   | Min. | Тур.  | Max. | Units |  |

|---------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------|---|------|-------|------|-------|--|

| Detection                                   |                       |                                                                                             |   |      |       |      |       |  |

| Detection on                                | $V_{DEN\_ON}$         | V <sub>DD</sub> rising                                                                      |   |      | 1.2   | 1.6  | V     |  |

| Detection off                               | V <sub>DEN_OFF</sub>  | V <sub>DD</sub> rising                                                                      |   |      | 12    | 7    | V     |  |

| DET Leakage Current                         | V <sub>DEN_LK</sub>   | $V_{DET}=V_{DD}=57V$ , Measure $I_{DET}$                                                    |   |      | 0.1   | 1    | uA    |  |

| Bias Current                                |                       | V <sub>DD</sub> =10.1V, float DEN pin,<br>not in Mark event, Measure<br>I <sub>SUPPLY</sub> |   | 0    | 5     | 12   | uA    |  |

|                                             |                       | V <sub>DD</sub> =1.6V, Measure I <sub>SUPPLY</sub>                                          | 4 | S    | 64    | 0    | uA    |  |

| Detection current                           | I <sub>DEN</sub>      | V <sub>DD</sub> =10.1V, Measure I <sub>SUPPLY</sub>                                         |   |      | 410   | 7    | uA    |  |

| Classification                              |                       |                                                                                             |   |      |       |      |       |  |

| Classification Stability Time <sup>5)</sup> | t <sub>SETUP</sub>    | 41 V                                                                                        |   |      | 150   |      | uS    |  |

| Classification Voltage                      | Vclass                | 13V <v<sub>DD&lt;21V<br/>1mA<i<sub>CLASS&lt;43mA</i<sub></v<sub>                            |   |      | 2.5   |      | V     |  |

|                                             |                       | 13V <v<sub>DD&lt;21V, Guaranteed by V<sub>CLASS</sub>, not tested in production</v<sub>     |   |      |       |      |       |  |

|                                             |                       | R <sub>CLASS</sub> =1270Ω,<br>13V <v<sub>DD&lt;21V</v<sub>                                  |   | ·    | 2     |      | mA    |  |

|                                             |                       | R <sub>CLASS</sub> =243Ω,<br>13V <v<sub>DD&lt;21V</v<sub>                                   |   |      | 10.55 |      | mA    |  |

| Classification Current                      | ICLASS                | R <sub>CLASS</sub> =137Ω,<br>13V <v<sub>DD&lt;21V</v<sub>                                   |   |      | 18.7  |      | mA    |  |

| <                                           |                       | R <sub>CLASS</sub> =90.9Ω,<br>13V <v<sub>DD&lt;21V</v<sub>                                  |   |      | 28.15 |      | mA    |  |

| A                                           |                       | R <sub>CLASS</sub> =62Ω, 13V <v<sub>DD&lt;21V</v<sub>                                       |   |      | 41    |      | mA    |  |

|                                             |                       | R <sub>CLASS</sub> = $0\Omega$ , $13V < V_{DD} < 21V$                                       |   |      | 60    |      | mA    |  |

| Classification Mark Threshold               | V <sub>Mark_th</sub>  | V <sub>DD</sub> rising                                                                      |   |      | 12    |      | V     |  |

| Classification Mark Threshold               | v mark_tn             | V <sub>DD</sub> falling                                                                     |   |      | 11.2  |      | V     |  |

| Classification Upper Threshold              | Vclsoff               | V <sub>DD</sub> rising                                                                      |   |      | 22    |      | V     |  |

| Classification Reset Threshold              | V <sub>Reset_th</sub> | V <sub>DD</sub> falling                                                                     |   |      | 5     |      | V     |  |

| Mark Event Current                          | I <sub>MARK</sub>     |                                                                                             |   |      | 1.5   |      | mA    |  |

| Mark Event Resistance                       | RMARK                 |                                                                                             |   |      | _     | 12   | kΩ    |  |

| IC Supply Current during Classification     | lin_class             |                                                                                             |   |      | 40    | 100  | uA    |  |

| Class Leakage Current                       | $I_{LKG}$             | V <sub>CLS</sub> =0V, V <sub>DD</sub> =57V,                                                 |   |      |       | 1    | uA    |  |

| PD UVLO                                     |                       |                                                                                             |   |      |       |      |       |  |

| VDD Turn on Threshold                       | Von                   | V <sub>DD</sub> -V <sub>SS</sub> rising                                                     |   |      | 35    |      | V     |  |

| VDD Turn off Threshold                               | Voff                 | V <sub>DD</sub> -V <sub>SS</sub> falling             |   |   | 31   |     | V  |

|------------------------------------------------------|----------------------|------------------------------------------------------|---|---|------|-----|----|

| IC Supply Current during Operation <sup>5)</sup>     | l <sub>IN</sub>      | V <sub>DD</sub> -V <sub>SS</sub> =57V                |   |   | 450  |     | uA |

| Pass Device and Current                              | Limit                |                                                      |   |   |      |     |    |

| On Resistance <sup>5)</sup>                          | R <sub>ON_RTN</sub>  | I <sub>RTN</sub> =600mA                              |   |   | 0.48 |     | Ω  |

| Leakage Current                                      | I <sub>RTN_LKG</sub> | V <sub>DD=</sub> V <sub>RTN=</sub> 57V               |   |   | 1    | 15  | uA |

| Current Limit                                        | I <sub>LIM</sub>     | VRTN=1V                                              |   |   | 530  |     | mA |

| Inrush Current Limit                                 | I <sub>INRUSH</sub>  | VRTN=2V                                              |   |   | 130  |     | mA |

| Inrush Current Termination <sup>5)</sup>             |                      | VRTN falling                                         |   |   | 1.2  | 1   | V  |

| Inrush to Operation Mode<br>Delay                    | TDELAY               |                                                      |   |   | 115  | 7   | mS |

| AMPS                                                 |                      |                                                      |   |   |      |     |    |

| Maintain Power Signature<br>Current Threshold        | V <sub>MPS</sub>     | R <sub>MPS</sub> =100Ω, 37V <v<sub>DD&lt;57V</v<sub> |   |   | 24   |     | V  |

| Maintain Power Signature<br>Current Limit            | IMPS_LIM             | R <sub>MPS</sub> =0Ω, 37V <v<sub>DD&lt;57V</v<sub>   | 4 | 6 | 25   | 9,  | mA |

| Auto MPS falling Current                             |                      | A                                                    |   |   | 42   | ~   | mA |

| threshold                                            | Hysteresis           |                                                      |   |   | 2    |     | mA |

| Maintain Power Signature<br>Duration                 | T <sub>MP</sub> s    | .1                                                   |   | 2 | 100  |     | mS |

| Maintain Power Signature<br>Period                   | Тмрро                |                                                      |   |   | 180  | 240 | mS |

| T2P                                                  |                      |                                                      | ~ |   |      |     |    |

| T2P Output Low Voltage                               |                      | V <sub>T2P</sub> =2mA, respect to VSS                |   |   | 0.1  | 0.3 | V  |

| T2P Output High Leakage<br>Current                   |                      | V <sub>T2P</sub> =48V                                | ) |   |      | 1   | uA |

| APD                                                  | 4                    | Y                                                    |   |   |      |     |    |

| APD High Threshold Voltage                           | V <sub>APD_H</sub>   | VDD-APD                                              |   |   | 1.5  |     | V  |

| APD Low Threshold Voltage                            | V <sub>APD_L</sub>   | VDD-APD                                              |   |   | 1    |     | V  |

| APD Leakage Current                                  |                      | VDD-APD=5V                                           |   |   |      | 2   | uA |

| VDD UVLO for APD                                     | V <sub>DD_UVLO</sub> | rising                                               |   |   | 7.5  |     | V  |

| Detection <sup>5)</sup>                              | V DD_UVLO            | falling                                              |   |   | 5.5  |     | V  |

| Protection                                           |                      |                                                      |   |   |      |     |    |

| Short circuit protection threshold <sup>5)</sup>     | Vsc                  |                                                      |   |   | 20   |     | V  |

| Short circuit protection deglitch time <sup>5)</sup> | tsc                  |                                                      |   |   | 0.5  |     | uS |

| Short circuit protection recover time <sup>5)</sup>  | tscr                 |                                                      |   |   |      | 10  | uS |

| Over current protection threshold <sup>5)</sup>      | V <sub>LIM</sub>     |                                                      |   |   | 10   |     | V  |

| Over current protection deglitch time <sup>5)</sup>  | toc                  |                                                      |   |   | 1.2  |     | mS |

| Thermal Shut down Temperature <sup>5)</sup>          | T <sub>PD_SD</sub>   |                                                      |   |   | 155  |     | °C |

| Thermal Shut down Hysteresis <sup>5)</sup>         | T <sub>PD_HYS</sub>   |                                              |       | 20   |    | °C |

|----------------------------------------------------|-----------------------|----------------------------------------------|-------|------|----|----|

| Adaptor detection deglitch time <sup>5)</sup>      | t <sub>APD</sub>      |                                              |       | 10   |    | mS |

| PD turn on deglitch time <sup>5)</sup>             | tpdon                 |                                              |       | 150  |    | uS |

| PD turn off deglitch time <sup>5)</sup>            | tpDOFF                |                                              |       | 10   |    | uS |

| State Machine deglitch time <sup>5)</sup>          | tsм                   |                                              |       | 10   |    | uS |

| Flyback Part                                       |                       |                                              |       |      |    |    |

| VDD Section (VDD Pin)                              |                       |                                              |       |      | 4  |    |

| Supply current from VDD pin                        | I <sub>HV</sub>       | VDD=12V, VCC=0V                              |       | 5    | 77 | mA |

| Leakage current of VDD pin                         | I <sub>VDD_LK</sub>   | VDD=57V, VCC=20V                             | (     | 20   |    | uA |

| VDD UVLO Section (UVLC                             | ) Pin)                | l                                            |       |      |    |    |

| VDD UVLO Threshold                                 | V <sub>UVLO_ON</sub>  | V <sub>UVLO</sub> rising                     | 4 6   | 1.2  | 0  | V  |

| UVLO Pin Floating Detection Current                | IUVLO_DET             | 4                                            | 7     | 5    |    | uA |

| UVLO Blanking Time                                 | T <sub>UVLO_BLK</sub> | Vuvlo=Vuvlo_on-0.4V                          | 0.5   |      | 1  | us |

| Supply Voltage Section (V                          | /CC Pin)              |                                              | A*. C |      |    |    |

| Turn-On Threshold<br>Voltage                       | Vcc_on                | VCC Rising, TA = 25°C                        |       | 8    |    | V  |

| Turn-Off Threshold<br>Voltage                      | Vcc_off               | VCC Falling, TA = 25°C                       |       | 5.5  |    | V  |

| Threshold Voltage for<br>Latch Release             | V <sub>CC_DLH</sub>   | Y                                            |       | 4.5  |    | V  |

| Startup Current                                    | Icc_st                | VCC=VCC_ON-0.5 V,<br>TA = 25°C               |       | 80   |    | uA |

| Operating Supply Current                           | I <sub>CC_OP</sub>    | VCC=6 V, C <sub>DRV</sub> =1nF,<br>fs=500kHz |       | 1.5  |    | mA |

| VCC OVP Clamp Current                              | I <sub>VCC_OVP</sub>  |                                              |       | 5    |    | mA |

| VCC OVP Voltage                                    | Vcc_ovp               |                                              |       | 16   |    | V  |

| VCC OVP Blanking Time                              | TVCC_OVP_BLK          |                                              |       | 100  |    | us |

| Working Mode Programm                              | ing Section (MC       | DDE Pin)                                     |       |      |    |    |

| Mode Pin Source Current                            | I <sub>MODE</sub>     |                                              |       | 40   |    | uA |

|                                                    | $V_{SSR}$             |                                              |       | 0.15 |    | V  |

| SSR Detection Threshold                            | - 0010                |                                              |       |      |    |    |

| SSR Detection Threshold  Voltage Sense Section (FI |                       |                                              |       |      |    |    |

|                                                    |                       |                                              |       | 2    |    | mA |

Unauthorized Photocopy and Duplication Prohibited.

| Output OVP threshold              | V <sub>FB_OVP</sub>   |                                |     |                                                | 1.45  |     | V      |

|-----------------------------------|-----------------------|--------------------------------|-----|------------------------------------------------|-------|-----|--------|

| Output OVP Debounce               | Nvs_ovp               |                                |     |                                                | 3     |     | Cycle  |

| Cycle Counts                      | TNV5_OVP              |                                |     |                                                | J     |     | Cycle  |

| Output OVP Hiccup Off             | T <sub>OVP_HIC</sub>  |                                |     |                                                | 60    |     | ms     |

| Time                              |                       |                                |     |                                                |       |     | _      |

| Current Sense Section (C          | S Pin)                |                                | 1   | 1                                              |       |     | 1      |

| Maximum Switching Current Limit   | I <sub>SW_max</sub>   |                                |     |                                                | 2.5   | 4   | Α      |

| Minimum Switching                 | I                     |                                |     |                                                | 0.6   |     | ^      |

| Current Limit                     | ISW_min               |                                |     |                                                | 0.6   | . ) | Α      |

| Leading-Edge Blanking Time        | t <sub>LEB</sub>      |                                |     |                                                | 150   |     | ns     |

| Primary side SCP                  | I <sub>SCP</sub>      |                                |     |                                                | 3     |     | Α      |

| Frequency Jittering Section       | on                    |                                | - / | 60                                             |       |     |        |

| Peak Jittering Amplitude          |                       |                                |     | 3                                              | 701   |     |        |

| to FB                             |                       |                                |     | $\mathcal{O}$                                  | ±7%   |     |        |

| Peak Jittering Frequency          | f <sub>PK_JIT</sub>   |                                |     |                                                | 33    |     | kHz    |

| Frequency Jittering               |                       |                                |     | (                                              | ±7%   |     |        |

| Amplitude                         |                       |                                |     |                                                | ±1 70 |     |        |

| Jittering Frequency               | f <sub>JIT</sub>      |                                |     |                                                | 200   |     | Hz     |

| DRV Section (DVR Pin)             |                       |                                | /   | >                                              |       |     |        |

| Maximum ON Duty                   | D <sub>ON_MAX</sub>   |                                | 7   |                                                | 70    |     | %      |

| Minimum ON Time                   | Ton_min               | Y 4                            |     |                                                | 150   |     | ns     |

| Maximum OFF Time                  | T <sub>OFF_MAX</sub>  | X                              |     |                                                | 40    |     | us     |

|                                   |                       | Constant in PSR or             |     |                                                | 500   |     | 1.11-  |

| Maximum Switching                 | f <sub>max</sub>      | SSR, $R_{MODE}$ =7.5 $k\Omega$ |     |                                                | 500   |     | kHz    |

| Frequency                         |                       | SSR, R <sub>MODE</sub> =37.5kΩ |     |                                                | 100   |     | kHz    |

| Minimum Switching                 |                       |                                |     |                                                | 00    |     | 1.1.1_ |

| Frequency                         | f <sub>min</sub>      | V                              |     |                                                | 30    |     | kHz    |

| COMP Section (COMP Pin            |                       |                                |     |                                                |       |     |        |

| Soft Start Time                   | Tss                   |                                |     |                                                | 12    |     | ms     |

| Open Pin Voltage                  | VCOMP_MAX             | Open Loop                      |     |                                                | 2.5   |     | V      |

| Internal Pull-Up Resistor         | R <sub>СОМР_</sub> UР |                                |     |                                                | 10    |     | kΩ     |

| OLP Hiccup On Time <sup>5)</sup>  | T <sub>OLP_ON</sub>   |                                |     |                                                | 6     |     | ms     |

| OLP Hiccup Off Time <sup>5)</sup> | T <sub>OLP_OFF</sub>  |                                |     |                                                | 60    |     | ms     |

| Internal Over Temperature         | e Protection          |                                |     | <u>.                                      </u> |       |     |        |

| Thermal Shutdown                  |                       |                                |     | •                                              |       |     |        |

9

| Threshold <sup>5)</sup>      |                  |  |    |    |

|------------------------------|------------------|--|----|----|

| OTP Hysteresis <sup>5)</sup> | T <sub>HYS</sub> |  | 30 | °C |

#### Note:

**5)** Guaranteed by design, not subject to test.

## **PIN DESCRIPTION**

| Pin                | Name  | Description                                                                            |

|--------------------|-------|----------------------------------------------------------------------------------------|

| 1                  | VDD   | Positive power supply terminal from PoE input power rail.                              |

| 2                  | AMPS  | Connect resistor from AMPS to VSS to program MPS current.                              |

| 3                  | DEN   | Connect a 24.9kΩ resistor between VDD and DEN for PoE detection.                       |

| 4                  | CLS   | Connect resistor from CLS to VSS to program classification current.                    |

|                    |       | Auxiliary power input detector. Use this pin for adaptor supply application. When the  |

| 5                  | APD   | voltage of VDD-APD is higher than V <sub>APD_H</sub> , the hot-swap MOSFET and CLS pin |

|                    |       | function is disabled, and the JWH7232 force T2P and PG active.                         |

| 6                  | FB    | Feedback pin for fly-back solution.                                                    |

| 7                  | COMP  | External compensation pin for SSR solution.                                            |

| 9, 16, 17          | GND   | Power Ground for fly-back circuit.                                                     |

| 10                 | VCC   | Supply bias voltage pin, powered through internal LDO from VIN. It is recommended to   |

| 10                 | VCC   | connect a 1uF capacitor between VCC and GND.                                           |

| 8, 11, 12, 15, 18, |       |                                                                                        |

| 20, 22, 23, 25,    | NC    | No connection.                                                                         |

| 27, 28             |       |                                                                                        |

| 13,14              | DRAIN | Internal fly-back MOSFET drain.                                                        |

|                    |       | Type 2 PSE indicator, open drain output.                                               |

| 19                 | T2P   | Pulled low to VSS indicates the presence of a Type 2 PSE or APD is enabled.            |

|                    |       | High impedance indicates a Type 1 PSE or no input.                                     |

| 21                 | RTN   | Drain of PD hot-swap MOSFET, connect GND to this pin.                                  |

| 24                 | VSS   | Negative power supply terminal from PoE input power rail.                              |

| 26                 | MODE  | PSR and SSR mode select pin.                                                           |

| 29                 | GND   | Exposed pad, connected to GND.                                                         |

## **BLOCK DIAGRAM**

## TYPICAL PERFORMANCE CHARACTERISTICS

TA = +25°C, unless otherwise noted

## PD FUNCTIONAL DESCRIPTION

The JWH7232 is an integrate IEEE 802.3af PoE complaint Powered Device (PD), it includes PD interface and high efficiency flyback converter.

The JWH7232 PD interface has all the functions

The JWH7232 PD interface has all the functions of IEEE 802.3af, including detection, classification, power up inrush and operation current limit as well as 100V Hot-swap MOSFET.

Compared with IEEE 802.3af, the IEEE 802.3at standard establishes a higher power allocation for PoE while maintaining the compatibility with the IEEE 802.3af systems. Power Sourcing Equipment (PSE) and Powered Device (PD) are defined as Type 1 complying with the IEEE 802.3af, or Type 2 complying with the IEEE 802.3at. the standard establishes a method of communication between PSE and PD with detection, classification and mark event.

The JWH7232 is one integrated PD solution with IEEE 802.3af PD interface and 13W DCDC converter.

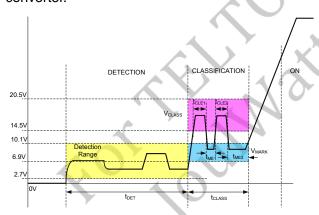

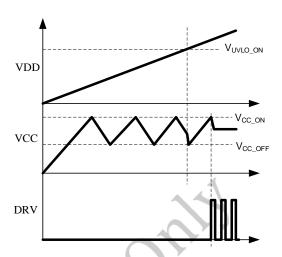

Figure 1. PD Interface Operation Description (2-Event Classification)

#### Detection

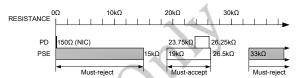

The R<sub>DET</sub> connected between DET and VDD pin is presented as a load to the PSE in Detection

Mode, when the input voltage is between 2.7V to 10.1V, the DET pin is pulled down to VSS and  $R_{DET}$  (24.9K $\Omega$ ±1%) is connected as the load of PSE. The detection resistance seen from PI is the result of the input bridge resistance in series with the VDD loading. The input bridge resistance is partially cancelled by JWH7232 effective leakage resistance during detection.

Figure 2. IEEE 802.3af Signature Resistance Ranges

#### Classification

#### 802.3af Classification

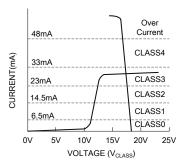

A PD can optionally present a classification signature to the PSE to indicate the maximum power it will draw while operating. The IEEE specification defines this signature as a constant current draw when the PSE port voltage is in the  $V_{\text{CLASS}}$  range (between 15.5V and 20.5V), with the current level indicating one of 5 possible PD classes. Figure 4 shows a typical PD load line, starting with the slope of the 25k $\Omega$  signature resistor below 10V, then transitioning to the classification signature current (in this case, Class 3) in the  $V_{\text{CLASS}}$  range.

Figure 3. PD Classification

JWH7232 presents a current in classification

mode as showing in Table 1.

**Table 1. CLASS Resistor Selection**

| Class | Max. Input<br>Power to<br>PD (W) | Classification<br>Current (mA) | $RcLass(\Omega)$ |

|-------|----------------------------------|--------------------------------|------------------|

| 0     | 12.95                            | 2-                             | 1270             |

| 1     | 3.84                             | 10.6                           | 243              |

| 2     | 6.49                             | 18.7                           | 137              |

| 3     | 12.95                            | 28.2                           | 90.9             |

| 4     | 25.5                             | 40.4                           | 62               |

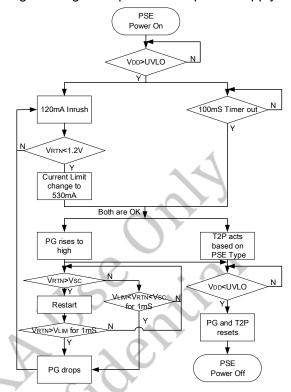

#### **PD Interface UVLO and Current Limit**

When PD is powered by PSE and  $V_{DD}$  is higher than turn on threshold, the Hot-swap switch will turn on with a limited current  $I_{INRUSH}$  to charge the downstream DCDC input capacitor  $C_{BULK}$ . The startup charging current is around 120mA. After the  $t_{DELAY}$  from UVLO starting, if RTN voltage drops to lower than 1.2V, Hot swap current limit will change to 530mA and the JWH7232 will assert PG signal and go from the startup mode to the running mode, the PG signal can enable downstream DCDC converter internally.

If  $V_{DD}$  drops below UVLO, the Hot-swap MOSFET and the DCDC converter both are disabled.

If output current is equal or higher than internal current limit, current limit loops works and  $V_{RTN}$  rise. when  $V_{LIM} < V_{RTN} < V_{SC}$ , the current limit timer starts counting, if the current limit timer expires, the current limit reverts to the inrush value, and PG is pulled down internally to disable DCDC regulator at the same time.

If  $V_{RTN}$ > $V_{SC}$ , the internal circuit shutdown the hot-swap MOS and returns on the MOS, the current limit timer runs. When the current limit timer expires, the current limit reverts to the inrush value, and PG is pulled down internally to disable DCDC regulator at the same time.

Figure 4 Shows the current, PG and T2P work

logic during startup from PSE power supply.

Figure 4. Startup Sequence

## **Maintain Power Signature**

In order to maintain power, the JWH7232 provide a valid Maintain Power Signature (MPS) at the PI (Power Interface).

If the PD MOS current is less than 40mA, an internal MPS timer starts counting, when the PD MOS current is larger than 40mA for  $t_{\text{MPS}}$ , the MPS timer reset until the current is less than 40mA again.

When the timer is larger than  $t_{MPDO}$ , the timer reset and the AMPS pin output  $V_{MPS}$  voltage for  $t_{MPS}$ , the PI sinks the maintain current  $I_{MPS}$ .

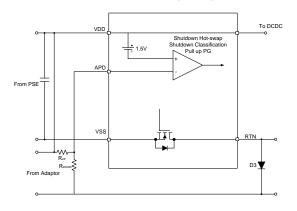

## Wall Power Adaptor Detection and Operation

For Applications where an auxiliary power

source such as a wall adaptor is used to power the device, the JWH7232 features wall power adaptor detection as showing in figure 5.

Figure 5. Adaptor Power Detection

There is a 1.5V reference voltage from  $V_{DD}$  to APD for adaptor detection. The adaptor is detected when APD voltage triggers:

$V_{DD}-V_{APD}=V_{ADPTOR}*R_{UP}/(R_{UP}+R_{DOWN})>1.5V$

If the adaptor voltage is much higher than the design adaptor voltage, VDD-VAPD will be high. If it is higher than 6.5V, the JWH7232 inner circuit will clamp the VDD-VAPD voltage at 6.5V, then a current will flow out through the APD pin, the current should be limited lower than 3mA by external resistor.

D3 is used to block reverse current between adaptor and PSE power source. When a wall adaptor is detected, the internal MOSFET between RTN and VSS turns off, classification current is disabled and T2P becomes active, the PG signal is active when adaptor is detected, so that it can enable the downstream DCDC converter even input hot-swap MOSFET is disabled.

#### **T2P Indicator**

The T2P signal is an open drain output. After  $t_{DELAY}$  from UVLO starting and RTN drops to 1.2V and a Type 2 PSE is detected, or a wall power adaptor is detected, the T2P signal will be pulled low to indicate a Type 2 PSE or an adaptor is detected.

### **Protection**

## Thermal Shutdown

Thermal shutdown is implemented to prevent the chip from thermally running away. JWH7232 has temperature monitor circuit for PD hot-swap MOSFET, when the PD temperature is higher than protection threshold, it will turn off the PD MOS and the PG signal is pulled low. The DCDC converter also stops working due to the PG signal is low.

When the temperature is lower than its recovery threshold, the chip is re-enabled and the PD MOS returns on slowly.

# DC/DC FUNCTIONAL DESCRIPTION

## Start-Up

## **VDD Start-Up**

When PG is high, the internal JFET turns on and a VDD current source starts to charge VCC cap. As soon as the VCC voltage reaches turn-on threshold  $V_{\text{CC}\_\text{ON}}$ , the controller is enabled and the converter starts switching. the internal startup circuit will be disabled when VCC reaches  $V_{\text{CC}\_\text{ON}}$ .

#### Soft-Start

In the absence of a detected fault, the controller begins to work normally along with soft start. The internal soft-start time is within 12ms with the COMP voltage  $V_{\text{COMP}}$  rising gradually from the minimum level to the maximum level. Every restart up is followed by a soft start.

## **Normal Operation**

After the controller start-up, it enters normal operation. There will be three working mode in JWH7232 for different application, SSR, PSR. The combination of resistor on MODE pin determines the working mode of JWH7232.

#### **Working Mode Selection**

At the initial 100us, the voltage on MODE pin and FB pin are detected to determine the working mode of the JWH7232. The default working mode is PSR mode. When PG is logical high and VCC reaches  $V_{\text{CC}\_\text{ON}}$ , the MODE pin voltage  $V_{\text{MODE}}$  is sensed to be compared with a

150mV internal reference voltage. If  $V_{\text{MODE}}$  is greater than 150mV, the JWH7232 will work in SSR mode, otherwise it will work in PSR mode. Then the working mode will be locked until the next VCC UVLO reset.

At the same time, FB voltage is compared with a 2V reference voltage to determine the output voltage sensing method.

In PSR mode, the output voltage is sensed for OVP and valley detection. In one method, FB is coupled to an auxiliary winding through a resistor divider to abstract output voltage information from Vaux. The initial FB voltage will be much smaller than 2V. This means the JWH7232 will work in PSR mode.

In SSR mode, the output voltage is sensed only for OVP. If the OVP protection is unnecessary in some application, FB pin will be floating, an initial 2uA pull-up current will pull the FB pin voltage greater than 2V. Otherwise, FB will be coupled to an auxiliary winding through a resistor divider to abstract output voltage information for OVP. The initial FB voltage will be much smaller than 2V in this case.

**Table 3. Working Mode Selection**

|      | ration of trontaining income concernant |      |                 |      |     |  |  |  |  |

|------|-----------------------------------------|------|-----------------|------|-----|--|--|--|--|

| Mode | Mode Pii<br>Voltage                     |      | FB Pin<br>Volta |      |     |  |  |  |  |

|      | Wiode                                   | Min. | Max.            | Min. | Max |  |  |  |  |

|      | SSR                                     | 150  |                 | 0    | 2   |  |  |  |  |

|      | SSR<br>without<br>OVP                   | 150  |                 | 2    |     |  |  |  |  |

|      | PSR                                     | 0    | 150             | 0    | 2   |  |  |  |  |

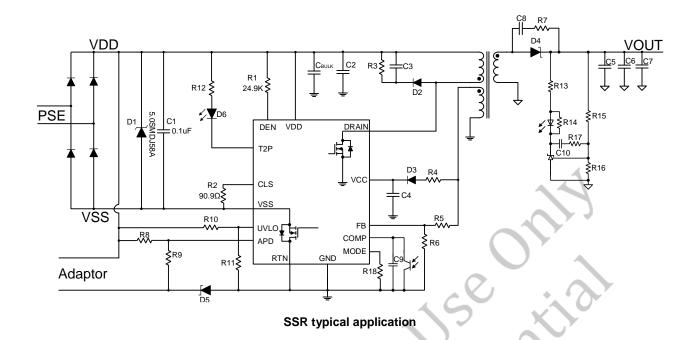

### **SSR Working Mode**

Figure 6. Typical application in SSR mode

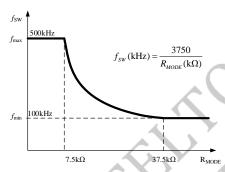

In SSR working mode, the maximum switching frequency  $f_{SW}$  can be programed by the external resistance  $R_{MODE}$  at MODE pin. The relationship between  $f_{SW}$  and  $R_{MODE}$  is shown in figure 7.

Figure 7. Switching frequency Vs. R<sub>MODE</sub> in SSR mode

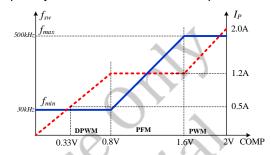

COMP JWH7232 According voltage, operates in different modes for efficiency optimization. It can be divided into four operation regions. Figure 8 illustrates the peak amplitude frequency and current modulation modes. Under heavy load condition, the system operates in PWM mode, the switching is fixed at a programmed maximum frequency, lpk will reduce from 2A to 1.6A. For medium-load range, the frequency modulation (PFM) is used to achieve high efficiency. When the load is further reduced, switching frequency is fixed at nominal 150kHz. Transitions between levels are automatically accomplished by the controller depending on the feedback voltage,  $V_{comp}$ . While working with no load or light load, the working frequency will further reduce from 150kHz to 30kHz. The minimum working frequency is set to 30kHz for noise prevention.

Figure 8. Switching frequency Vs. V<sub>COMP</sub> in SSR mode

## **PSR Working Mode**

JWH7232 can also be used in PSR applications as figure 9 shows.

Figure 9. Typical application in PSR mode

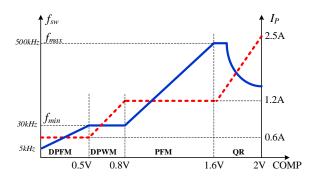

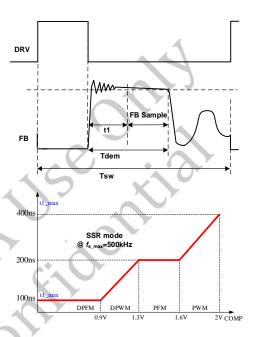

In PSR mode, JWH7232 behaves as a multi-mode QR controller with primary-side regulation. According to the compensation voltage  $V_{comp}$ , which regulated by the output voltage, the converter operates in different modes for efficiency optimization. Figure.10

illustrates the frequency and peak current amplitude modulation modes. It can be divided into four operation regions as shown in figure 10.

Figure 10. Switching frequency Vs. V<sub>COMP</sub> in PSR mode

Under heavy load condition, the system operates in QR mode, the maximum switching frequency is limited to 500kHz. medium-load range, the Pulse Frequency Modulation (PFM) is used and primary peak current is fixed to achieve high efficiency. When the load is further reduced, switching frequency is fixed at nominal 150kHz along with primary peak current varying from 48% to 24% of its maximum. While working with no load or light load, the working frequency will further reduce from 150kHz to 30kHz. The minimum working frequency is set to 30kHz for noise prevention. In PSR mode, the compensation network is set up internally, so the COMP pin will be floating.

## **Output Voltage Sensing**

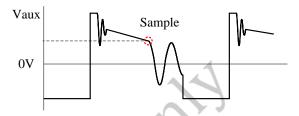

In PSR mode, the output voltage Vo is sensed on the auxiliary winding when the magnetizing current transferred to the secondary side in PSR mode.

The waveform of a typical auxiliary winding voltage in QR mode is shown in figure 14. The accuracy of the output voltage is depended on how to get the voltage signal when inductor

current reaches zero. One method is using internal dv/dt detection to detect the inflection point of Vaux during gate off. At this point, the secondary side current is approximately zero, and Vaux represents the output voltage.

Figure 11. Typical auxiliary winding voltage Vaux waveform in QR mode.

## Other Functions and Features

## **Frequency Jittering**

To achieve good EMI performance, frequency jittering method is integrated in JWH7232. The frequency jittering in QR operation is achieved by peak current perturbation. The peak current is varied by  $\pm 7\%$  around its normal value. And in other operation modes, the frequency jittering is achieved by varying the switching frequency directly. The variation is  $\pm 7\%$  around its normal value. The modulation cycle is constant 200Hz for noise prevention.

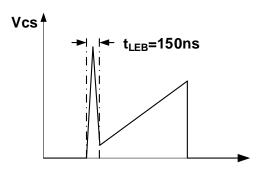

## Lead Edge Blanking (LEB)

In order to avoid the premature termination of the switching pulse due to the parasitic capacitance, an internal leading-edge blanking (LEB) is used between the CS pin and the current comparator input. The current comparator is disabled and can't turn off the external MOSFET during the blanking time. The normal LEB time is around 150ns. Figure 12 shows the leading edge blanking time.

Figure 12. LEB blanking

## **CCM Preventing in PSR Mode**

The JWH7232 working in PSR mode, when the primary-side peak current exceeds the value decided by the compensation voltage  $V_{comp}$ , the switch turns off. When the controller detects ZCD signal and the switch period exceeds frequency-limit signal, the switch turns on. But the ZCD signal may not be detected during start-up moment because of low output voltage, then the switch will turn on after 40us to make sure the system operates in DCM.

Under light load condition, if ZCD signal has been detected before the frequency-limit signal, the switch will be turned on in 6us after the frequency-limit signal.

## **FB Blanking Time**

In order to improve the output voltage detection accuracy and avoid the turn on spike interference, a FB blanking time is set. The FB voltage will be sensed after blanking time as figure 13 shows.

Since the transformer inductance will be greatly different with different maximum switching frequencies in SSR mode, the blanking time also needs to vary with the maximum frequency. The maximum working frequency is divided into two frequency region. When maximum working

frequency is in high region (higher than 250kHz and lower than 500kHz), the maximum blanking time is 0.4us; when maximum working frequency is in low region (higher than 100kHz and lower than 250kHz), the maximum blanking time is 1.2us

Figure 13. LEB blanking

#### **Minimum Load Requirement**

In order to sample the isolated output voltage from the primary-side flyback pulse waveform in PSR mode, the JWH7232 has to turn on and off at least for a minimum amount of time and with a minimum frequency. The JWH7232 delivers a minimum amount of energy even during light load conditions to ensure accurate output voltage information. The minimum energy delivery creates a minimum load requirement, which can be approximately estimated as:

$$I_{O(MIN)} = \frac{L_m \cdot I_{SW(MIN)}^2 \cdot f_{MIN}}{2V_o}$$

(3)

Where, L<sub>m</sub> is the transformer primary inductance,

$I_{SW(MIN)}$  is the minimum switch current limit,  $f_{MIN}$  is the minimum switch frequency.

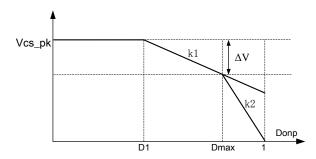

## **Slope Compensation in SSR Mode**

For current mode control applications in SSR mode, the duty cycle can exceed 50%. For duty cycles greater than 50 percent, current mode control circuits are subject to sub-harmonic oscillation. Therefore, a slope compensation is needed. Typically, D1=0.4, deltaV=1/4\*V<sub>CS\_PK</sub>.

Figure 14. Slope compensation

#### **Protection**

### **VDD UVLO**

UVLO pin is coupled to VDD pin via a resistor divider to monitor the input voltage for UVLO protection. When UVLO pin voltage V<sub>UVLO</sub> is higher than a VDD UVLO threshold V<sub>UVLO</sub>ON (typically 1.2V), the controller is enabled to switching. And the controller is disabled when VDD voltage is lower than V<sub>UVLO</sub>ON for UVLO blanking time (1us typically).

During start up, if VDD voltage is below  $V_{UVLO\_ON}$  when VCC reaches  $V_{CC\_ON}$ , the controller will restart until VDD voltage reaches  $V_{UVLO\_ON}$ . Once it occurs, VCC voltage will be pull-down quickly to restart, and the controller will start at the next time when VCC reaches  $V_{CC\_ON}$  as shows.

Figure 15. VDD UVLO

## **Primary Side SCP**

The JWH7232 always operates with cycle-by-cycle primary-peak current control. The normal operating range of the primary side current is 0.6 to 2.5A. If the primary side current exceeds the 3A SCP threshold after an internal shorter leading-edge blanking time (typical 110ns) for three consecutive cycles, the device shuts down, and then the UVLO reset and re-start fault cycle begins.

#### **Output OVP (FB OVP)**

The voltage output over protection determined by the voltage feedback on the FB pin. If the voltage sample on FB exceeds 1.45V for three consecutive switching cycles, an FB\_OVP fault is asserted, and then the device shuts down, the UVLO reset and re-start fault cycle begins. In PSR2 mode without auxiliary winding, FB pin is coupled to SW pin through a feedback resistor R<sub>FB</sub>, the output voltage can be represented by the current IFB flow through RFB. If IFB is greater than a current threshold (typically, 120uA) for three consecutive switching cycles, an FB OVP fault is asserted.

#### **VCC OVP**

If the voltage on VCC pin continues exceeds the Over-Voltage protection threshold (typically, 16V) more than 100us, a VCC OVP fault is asserted. The device shuts down, then the UVLO reset and re-start fault cycle begins.

#### **OLP**

While working with heavy load, if the primary side current continues to reach the maximum current for 6ms, an OLP fault is asserted. The device shuts down, and the hiccup off time is 60ms.

#### **Internal OTP**

The internal over temperature protection threshold is 150°C. If the junction temperature of the device reaches this threshold, the device shuts down. When the junction temperature falls below 120°C, the device initiates the UVLO reset and re-start fault cycle.

## PACKAGE OUTLINE

## **IMPORTANT NOTICE**

Joulwatt Technology Inc. reserves the right to make modifications, enhancements, improvements,

corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Inc. does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Copyright © 2021 JWH7232 Incorporated.

All rights are reserved by Joulwatt Technology Inc.