Overvoltage and IEC ESD Protection

### 1. General Description

The WP5602 is a USB Type-C port protection chip that provides 20-V Short-to-VBUS overvoltage and IEC ESD protection.

By integrating low on-resistance power switch and low capacitance TVS, the WP5602 protects USB Type-C ports CC, SBU and D+/D- that undergoing overvoltage and IEC 61000-4-2 system level ESD without interfering with normal operation.

#### 2. Features

- Short to VBUS Overvoltage Protection for CC1, CC2. SBU1 and SBU2

- IEC 61000-4-2 ESD Protection for CC1, CC2, SBU1, SBU2, DP, DM

- Low on-resistance protection FET for CC1 and CC2 passing 600 mA V<sub>CONN</sub> current

- Fast OVP response for CCX and SBUX

- CC Dead Battery Resistors integrated for handling dead battery use case in mobile devices

- Package: 3-mm × 3-mm WQFN

#### 3. Applications

- Laptop PC

- Tablets

- Smart phones

- Monitors and TVS

- **Docking Stations**

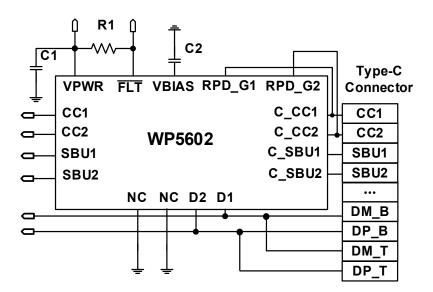

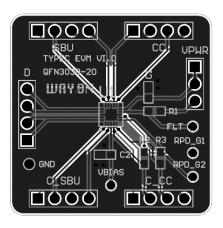

### 4. Typical Application

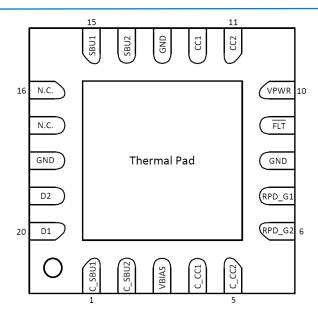

## **5. Pin Configuration**

## 6. Pin Description

| PIN NUMBER | PIN<br>NAME | I/O   | PIN FUNCTIONS                                                                                                                                            |  |  |  |

|------------|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | C_SBU1      | I/O   | Connector side of the SBU1 OVP FET. Connect to either SBU pin of the USB Type-C connector.                                                               |  |  |  |

| 2          | C_SBU2      | I/O   | Connector side of the SBU2 OVP FET. Connect to either SBU pin of the USB Type-C connector.                                                               |  |  |  |

| 3          | VBIAS       | Power | Pin for ESD support capacitor. Place a 0.1-µF capacitor on this pin to ground.                                                                           |  |  |  |

| 4          | C_CC1       | I/O   | Connector side of the CC1 OVP FET. Connect to either CC pin of the USB Type-C connector.                                                                 |  |  |  |

| 5          | C_CC2       | I/O   | Connector side of the CC2 OVP FET. Connect to either CC pin of the USB Type-C connector.                                                                 |  |  |  |

| 6          | RPD_G2      | I/O   | Short to C_CC2 if dead battery resistors are needed. If dead battery resistors are not needed, short pin to GND.                                         |  |  |  |

| 7          | RPD_G1      | I/O   | Short to C_CC1 if dead battery resistors are needed. If dead battery resistors are not needed, short pin to GND.                                         |  |  |  |

| 8          | GND         | GND   | Ground.                                                                                                                                                  |  |  |  |

| 9          | FLT         | 0     | Open drain for fault reporting. Under over temperature & over voltage conditions, pull low. Otherwise stay high-Z. Connect to VPWR by external resistor. |  |  |  |

| 10         | VPWR        | Power | 2.7V – 5.5V power supply.                                                                                                                                |  |  |  |

| PIN NUMBER | PIN NAME       | I/O | PIN FUNCTIONS                                                                             |

|------------|----------------|-----|-------------------------------------------------------------------------------------------|

| 11         | CC2            | I/O | System side of the CC2 OVP FET. Connect to either CC pin of the CC/PD controller.         |

| 12         | CC1            | I/O | System side of the CC1 OVP FET. Connect to either CC pin of the CC/PD controller.         |

| 13         | GND            | GND | Ground.                                                                                   |

| 14         | SBU2           | I/O | System side of the SBU2 OVP FET. Connect to either SBU pin of the SBU MUX.                |

| 15         | SBU1           | I/O | System side of the SBU1 OVP FET. Connect to either SBU pin of the SBU MUX.                |

| 16         | NC             | I/O | Unused pin. Connect to Ground.                                                            |

| 17         | NC             | I/O | Unused pin. Connect to Ground.                                                            |

| 18         | GND            | GND | Ground.                                                                                   |

| 19         | D2             | I/O | USB2.0 IEC ESD protection. Connect to any of the USB2.0 pins of the USB Type-C connector. |

| 20         | D1             | I/O | USB2.0 IEC ESD protection. Connect to any of the USB2.0 pins of the USB Type-C connector. |

| -          | Thermal<br>Pad | GND | Internally connected to GND. Used as a heatsink. Connect to the PCB GND plane.            |

### 7. Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>[1]</sup>

|                 | PARAMETER                      | RATING     | UNIT |

|-----------------|--------------------------------|------------|------|

| land Malkana    | VPWR                           | -0.3 to 6  | V    |

| Input Voltage   | RPD_G1, RPD_G2                 | -0.3 to 24 | V    |

| Outrout Valtage | FLT                            | -0.3 to 6  | V    |

| Output Voltage  | VBIAS                          | -0.3 to 24 | V    |

|                 | D1, D2                         | -0.3 to 6  | V    |

| I/O Voltage     | CC1, CC2, SBU1, SBU2           | -0.3 to 6  | V    |

|                 | C_CC1, C_CC2, C_SBU1, C_SBU2   | -0.3 to 24 | V    |

| Operat          | Operating Free Air Temperature |            | °C   |

| S               | torage Temperature             | -65 to 150 | °C   |

**NOTE [1]:**Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 8. ESD Ratings—JEDEC Specification

|                         | PARAMETER                                                                | VALUE | UNIT |

|-------------------------|--------------------------------------------------------------------------|-------|------|

|                         | Human-Body Model (HBM),<br>Per ANSI/ESDA/JEDEC JS-001 <sup>[2]</sup>     | ±6000 | V    |

| Electrostatic Discharge | Charged-Device Model (CDM),<br>Per ANSI/ESDA/JEDEC JS-002 <sup>[3]</sup> | ±2000 | V    |

|                         | Latch-up model, per JEDEC JESD78F-2022                                   | ±800  | mA   |

**NOTE [2]:** JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2000 V may actually have higher performance.

**NOTE [3]:** JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±500 V may actually have higher performance.

## 9. ESD Ratings—IEC Specification

|                     | PARAMETER               |                      | VALUE  | UNIT |

|---------------------|-------------------------|----------------------|--------|------|

| Electrostatic       | IEC 64000 4 2 D4 D2     | Contact Discharge    | ±15000 |      |

|                     | IEC 61000-4-2, D1, D2   | Air-gap Discharge    | ±30000 |      |

|                     | IEC 61000-4-2, C_CC1,   | Contact Discharge    | ±10000 | V    |

| Discharge           | C_CC2                   | Air-gap Discharge    | ±20000 | V    |

|                     | IEC 61000-4-2, C_SBU1,  | Contact Discharge    | ±10000 |      |

|                     | C_SBU2                  | Air-gap Discharge    | ±20000 |      |

| Lightning and Surge | IEC 61000-4-5, C_CC1, C | _CC2, C_SBU1, C_SBU2 | ±50    | V    |

### 10. Recommended Operating Conditions

(Over operating free-air temperature range, unless otherwise noted)

| SYMBOL             | PARAMETER                             |                                                                                                                | MIN  | TYP. | MAX  | UNIT |

|--------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                    | Innut Valtage                         | VPWR                                                                                                           | 2.7  | 3.3  | 5.5  | V    |

| V <sub>IN</sub>    | Input Voltage                         | RPD_G1, RPD_G2                                                                                                 | 0    |      | 5.5  | V    |

| V <sub>OUT</sub>   | FLT Pull-u                            | Resistor Power Rail                                                                                            | 2.7  |      | 5.5  | V    |

|                    |                                       | D1, D2                                                                                                         | -0.3 |      | 5.5  | V    |

| V <sub>IO</sub>    | I/O Voltage                           | CC1, CC2, C_CC1,<br>C_CC2                                                                                      | 0    |      | 5.5  | V    |

|                    |                                       | SBU1, SBU2, C_SBU1,<br>C_SBU2                                                                                  | 0    |      | 4.3  | V    |

| Ivconn             | V <sub>CONN</sub> Current             | Current flowing into<br>CC1/2 and flowing out of<br>C_CC1/2,<br>V <sub>CCX</sub> – V <sub>C_CCX</sub> ≤ 250 mV |      |      | 600  | mA   |

| I <sub>VCONN</sub> | V <sub>CONN</sub> Current             | Current flowing into<br>CC1/2 and flowing out of<br>C_CC1/2, T <sub>J</sub> ≤ 105°C                            |      |      | 1.25 | А    |

|                    |                                       | FLT Pull-up Resistance                                                                                         | 1.7  |      | 300  | kΩ   |

|                    | External<br>Components <sup>[4]</sup> | VBIAS Capacitance <sup>[5]</sup>                                                                               |      | 0.1  |      | μF   |

|                    |                                       | VPWR Capacitance                                                                                               | 0.3  | 1    |      | μF   |

**NOTE [4]:** For recommended values for capacitors and resistors, the typical values assume a component placed on the board near the pin. Minimum and maximum values listed are inclusive of manufacturing tolerances, voltage derating, board capacitance, and temperature variation. The effective value presented must be within the minimum and maximums listed in the table.

**NOTE [5]:** The VBIAS pin requires a minimum 35-V<sub>DC</sub> rated capacitor. A 50-V<sub>DC</sub> rated capacitor is recommended to reduce capacitance derating. See the VBIAS Capacitor Selection section for more information on selecting the VBIAS capacitor.

### 11. Electrical Characteristics

(Over operating free-air temperature range, unless otherwise noted)

| SYMBOL                                | PARAMETER                                                                                                               | TEST CONDITIONS                                                                                                                                          | MIN  | TYP. | MAX | UNIT |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| CC OVP Sv                             | witches                                                                                                                 |                                                                                                                                                          |      | '    | '   |      |

| Ron                                   | On resistance of CC<br>OVP FETs,<br>T <sub>J</sub> ≤ 85 °C                                                              | CCX = 5.5 V                                                                                                                                              |      | 300  | 600 | mΩ   |

| R <sub>ONFLAT</sub>                   | On resistance flatness                                                                                                  | Sweep CCX voltage between 0V and1.2V                                                                                                                     |      |      | 5   | mΩ   |

| C <sub>ON_CC</sub>                    | Equivalent on capacitance                                                                                               | Capacitance from C_CCX or CCX to GND. $V_{C_CCX}/V_{CCX} = 0 \text{ V to } 1.2 \text{ V,}$ $f = 400 \text{ kHz}$                                         | 30   | 74   | 90  | pF   |

| $R_{	extsf{D}_{	extsf{D}}	extsf{DB}}$ | Dead battery pull-down resistance (only present when device is unpowered). Effective resistance of RD and FET in series | V <sub>C_CCX</sub> = 2.6 V                                                                                                                               | 4.1  | 5.1  | 6.1 | ΚΩ   |

| $V_{TH\_DB}$                          | Threshold voltage of<br>the pulldown FET in<br>series with RD during<br>dead battery                                    | I <sub>CC</sub> = 80 μA                                                                                                                                  | 0.5  | 0.9  | 1.2 | V    |

| Vovecc                                | OVP threshold on CC pins                                                                                                | Place 5.5 V on C_CCX.  Step up C_CCX until the FLT pin is asserted                                                                                       | 5.75 | 6    | 6.2 | V    |

| Vovpcc_hys                            | Hysteresis on CC OVP                                                                                                    | Place 6.5 V on C_CCX. Step down the voltage on C_CCX until the FLT pin is deasserted. Measure difference between rising and falling OVP threshold for CC |      | 50   |     | mV   |

| BW <sub>ON</sub>                      | On bandwidth single<br>ended<br>(–3 dB)                                                                                 | Measure the –3-dB<br>bandwidth from C_CCX to<br>CCX. Single ended<br>measurement, 50Ω system<br>V <sub>CM</sub> = 0.1 V to 1.2 V                         |      | 100  |     | MHz  |

| V <sub>STBUS</sub> _                  | Short-to-VBUS<br>tolerance on the CC<br>pins                                                                            | Hot-Plug C_CCX with a<br>1meter USB Type C Cable,<br>place a 30-Ω load on CCX                                                                            |      |      | 24  | V    |

| SYMBOL                 | PARAMETER                                                              | TEST CONDITIONS                                                                                                                                            | MIN | TYP. | MAX  | UNIT |

|------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| Vstbus_<br>cc_clamp    | Short-to-VBUS system-<br>side clamping voltage<br>on the CC pins (CCX) | Hot-Plug C_CCX with a 1-<br>meter USB Type C Cable.<br>Hot-Plug voltage C_CCX =<br>24 V. VPWR = 3.3 V. Place a<br>30Ω load on CCX                          |     | 8    |      | V    |

| SBU OVP                | Switches                                                               |                                                                                                                                                            |     |      |      |      |

| R <sub>ON</sub>        | On resistance of SBU  OVP FETs                                         | SBUX = 3.6 V,<br>-40°C ≤ T <sub>J</sub> ≤ +85°C                                                                                                            |     | 3.5  | 6.5  | Ω    |

| Ronflat                | On resistance flatness                                                 | Sweep SBUX voltage<br>between 0 V and 3.6 V.<br>–40°C ≤ T <sub>J</sub> ≤ +85°C                                                                             |     | 1    | 1.5  | Ω    |

| C <sub>ON_</sub> SBU   | Equivalent on capacitance                                              | Capacitance from SBUX or C_SBUX to GND. Measure at V <sub>C_SBUX</sub> /V <sub>SBUX</sub> = 0.3 V to 3.6 V                                                 |     | 9    |      | pF   |

| V <sub>OVPSBU</sub>    | OVP threshold on SBU pins                                              | Place 3.6 V on C_SBUX.  Step up C_SBUX until the  FLT pin is asserted                                                                                      | 4.3 | 4.5  | 4.75 | V    |

| Vovpsbu<br>_HYS        | Hysteresis on SBU<br>OVP                                               | Place 5 V on C_CCX. Step down the voltage on C_CCX until the FLT pin is deasserted. Measure difference between rising and falling OVP threshold for C SBUX |     | 60   |      | mV   |

| BW <sub>ON</sub>       | On bandwidth single<br>ended (–3 dB)                                   | Measure the –3-dB bandwidth from C_SBUX to SBUX. Single ended measurement, 50-Ω system. V <sub>CM</sub> = 0.1 V to 3.6 V                                   |     | 1000 |      | MHz  |

| X <sub>TALK</sub>      | Crosstalk                                                              | Measure crosstalk at f = 1 MHz from SBU1 to C_SBU2 or SBU2 to C_SBU1. $V_{CM1}$ = 3.6 V, $V_{CM2}$ =0.3V. Be sure to terminate open sides to 50 $\Omega$   |     | -80  |      | dB   |

| V <sub>STBUS_SBU</sub> | Short-to-VBUS<br>tolerance on the SBU<br>pins                          | Hot-Plug C_SBUX with a 1-<br>meter USB Type C Cable.<br>Put a 40Ω resistor to GND on<br>SBUX                                                               |     |      | 24   | V    |

| SYMBOL                        | PARAMETER                                                                   | TEST CONDITIONS                                                                                                                                                                                                         | MIN | TYP. | MAX | UNIT |

|-------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Vstbus_sbu<br>_CLAMP          | Short-to-VBUS system-<br>side clamping voltage<br>on the SBU pins<br>(SBUX) | Hot-Plug C_SBUX with a 1-<br>meter USB Type C Cable.<br>Hot-Plug voltage $V_{C\_SBUX}$ = 24 V. $V_{PWR}$ = 3.3 V. Put a 40Ω resistor to GND on SBUX                                                                     |     | 8    |     | V    |

| Power Su                      | pply and Leakage Cui                                                        | rrents                                                                                                                                                                                                                  |     |      |     |      |

| V <sub>PWR_UVLO</sub>         | VPWR under voltage<br>lockout                                               | Place 1 V on VPWR and raise voltage until SBU or CC FETs turn on                                                                                                                                                        | 2.1 | 2.3  | 2.5 | V    |

| V <sub>PWR_UVLO</sub><br>_HYS | VPWR UVLO<br>hysteresis                                                     | Place 3 V on VPWR and lower voltage until SBU or CC FETs turnoff; measure difference between rising and falling UVLO to calculate hysteresis                                                                            |     | 10   |     | mV   |

| $I_{VPWR}$                    | VPWR supply current                                                         | V <sub>PWR</sub> = 3.3 V (Typical),<br>–40°C ≤ T <sub>J</sub> ≤ +85°C.                                                                                                                                                  |     | 70   | 120 | μA   |

| I <sub>CC_LEAK</sub>          | Leakage current for CC pins when device is powered                          | V <sub>PWR</sub> = 3.3 V, V <sub>C_CCX</sub> = 3.6 V,<br>CCX pins are floating,<br>measure leakage into<br>C_CCX pins. Result must be<br>same if CCX side is biased<br>and C_CCX is left floating.                      |     |      | 5   | μА   |

| I <sub>SBU_LEAK</sub>         | Leakage current for<br>SBU pins when device<br>is powered                   | V <sub>PWR</sub> = 3.3 V, V <sub>C_SBUX</sub> = 3.6V, SBUX pins are floating, measure leakage into C_SBUX pins. Result must be same if SBUX side is biased and C_SBUX is left floating.  -40°C ≤ T <sub>J</sub> ≤ 85°C. |     |      | 3.5 | μA   |

| Ic_cc_leak<br>_ovp            | Leakage current for CC pins when device is in OVP                           | V <sub>PWR</sub> = 0 V or 3.3 V, V <sub>C_CCX</sub> = 24V, CCX pins are set to 0 V,  Measure leakage into  C_CCX pins                                                                                                   |     |      | 200 | μA   |

| SYMBOL                  | PARAMETER                                                | TEST CONDITIONS                                                                                                                  | MIN | TYP. | MAX | UNIT |

|-------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Ic_sbu_leak_<br>ovp     | Leakage current for<br>SBU pins when device<br>is in OVP | V <sub>PWR</sub> = 0 V or 3.3 V, V <sub>C_SBUX</sub> = 24 V, SBUX pins are set to 0 V, measure leakage into C_SBUX pins          |     |      | 200 | μΑ   |

| ICC_LEAK<br>_OVP        | Leakage current for CC pins when device is in OVP        | V <sub>PWR</sub> = 0 V or 3.3 V, V <sub>C_CCX</sub> = 24 V, CCX pins are set to 0 V, measure leakage out of CCX pins             |     |      | 30  | μΑ   |

| ISBU_LEAK<br>_OVP       | Leakage current for<br>SBU pins when device<br>is in OVP | V <sub>PWR</sub> = 0 V or 3.3 V, V <sub>C_SBUX</sub><br>= 24 V, SBUX pins are set to<br>0 V, measure leakage out of<br>SBUX pins | -1  |      | 1   | μΑ   |

| I <sub>DX_LEAK</sub>    | Leakage current for Dx pins                              | V <sub>DX</sub> = 3.6 V, measure<br>leakage into Dx pins                                                                         |     |      | 1   | μA   |

| FLT Pin                 |                                                          |                                                                                                                                  |     |      |     |      |

| Vol                     | Low-level output<br>voltage                              | $I_{OL}$ = 3 mA.  Measure the voltage at the FLT pin                                                                             |     |      | 0.4 | V    |

| Over Tem                | perature Protection                                      |                                                                                                                                  |     |      |     |      |

| T <sub>SD_RISING</sub>  |                                                          | erature protection shutdown                                                                                                      |     | 170  |     | °C   |

| T <sub>SD_FALLING</sub> |                                                          | erature protection shutdown<br>nreshold                                                                                          |     | 135  |     | °C   |

| T <sub>SD_HYST</sub>    |                                                          | orotection shutdown threshold<br>ysteresis                                                                                       |     | 35   |     | °C   |

| Dx ESD P                | rotection                                                |                                                                                                                                  |     |      |     |      |

| V <sub>RWM_POS</sub>    | Reverse stand-off<br>voltage from Dx<br>to GND           | Dx to GND. IDX ≤1 μA                                                                                                             |     |      | 5.5 | V    |

| $V_{ m RWM\_NEG}$       | Reverse stand-off<br>voltage from GND<br>to Dx           | GND to Dx                                                                                                                        |     |      | 0   | V    |

| $V_{BR\_POS}$           | Break-down voltage from Dx to GND                        | Dx to GND. IBR = 1 mA                                                                                                            | 7   |      |     | V    |

| $V_{BR\_NEG}$           | Break-down voltage from GND to Dx                        | GND to Dx. IBR = 8 mA                                                                                                            | 0.6 |      |     | V    |

| SYMBOL                       | PARAMETER                                    | TEST CONDITIONS                                                                                                                 | MIN  | TYP. | MAX | UNIT |

|------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| C <sub>IO</sub>              | Capacitance Dx to<br>GND or GND to Dx        | f = 1 MHz, VIO = 2.5 V                                                                                                          |      | 2.5  |     | pF   |

| ΔC <sub>IO</sub>             | Differential capacitance between two Dx pins | f = 1 MHz, VIO = 2.5 V                                                                                                          |      | 1    |     | pF   |

| $R_{DYN}$                    | Dynamic on-resistance<br>Dx IEC clamps       | Dx to GND or GND to Dx                                                                                                          |      | 0.4  |     | Ω    |

| Power-On                     | and Off Timings                              |                                                                                                                                 |      |      |     |      |

| t <sub>ON</sub>              | _                                            | ng VPWR UVLO until CC and<br>'P FETs are on                                                                                     |      | 0.15 |     | ms   |

| t <sub>ON_DB</sub>           | SBU OVP FETs are on                          | ng VPWR UVLO until CC and and the dead battery resistors turned off                                                             |      | 5.7  |     | ms   |

| $\frac{dV_{PWR\_OFF}}{/d_t}$ |                                              | ved to guarantee CC and SBU<br>during a power off                                                                               | -0.5 |      |     | V/µs |

| Over Volta                   | age Protection                               |                                                                                                                                 |      |      |     |      |

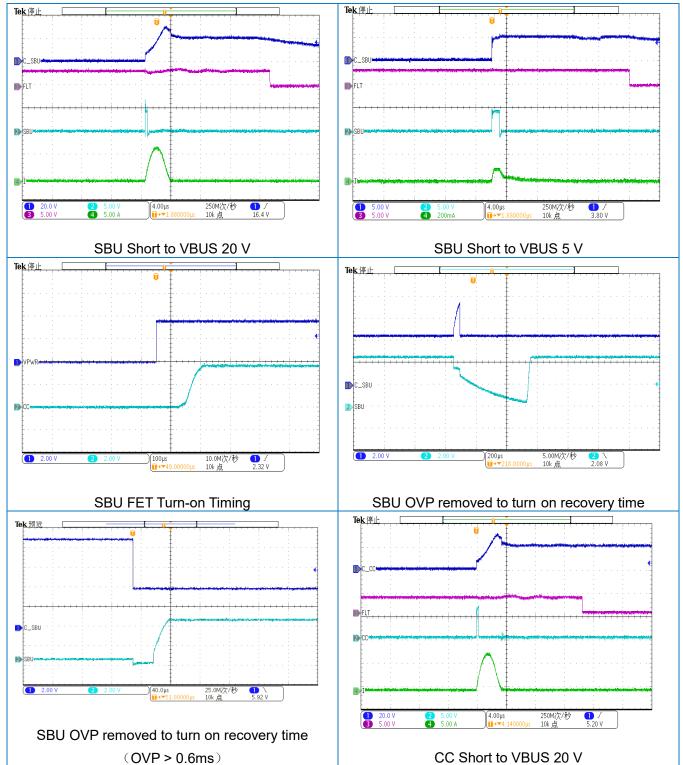

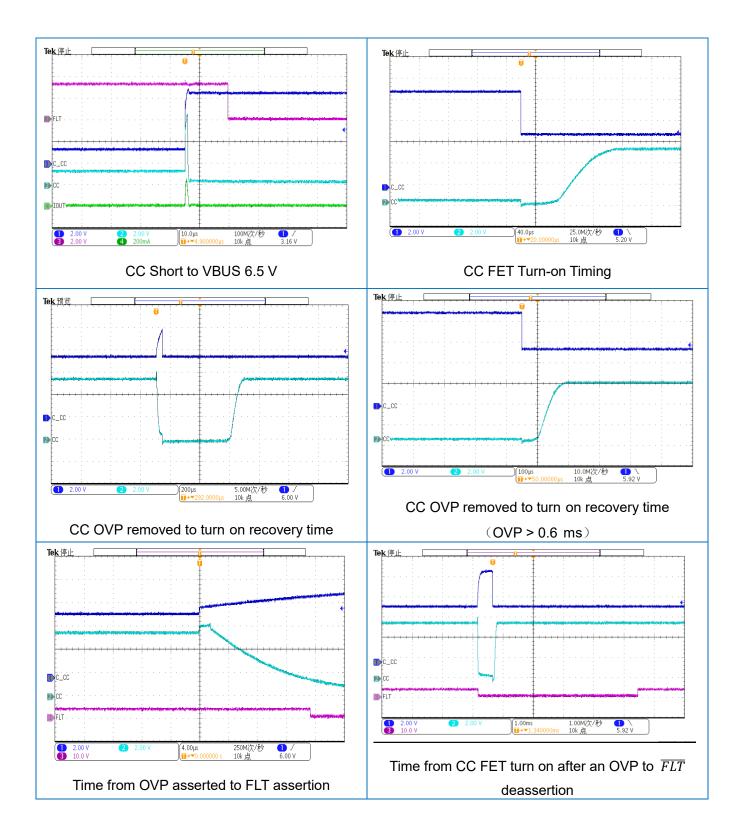

| tovp_respon                  | · ·                                          | the CC pins. Time from OVP il OVP FETs turnoff                                                                                  |      | 80   |     | ns   |

| t <sub>OVP_RESPON</sub>      | ·                                            | the SBU pins. Time from OVP                                                                                                     |      | 130  |     | ns   |

| tovp_recove<br>ry_cc_1       | occurred, the minimum t                      | ne CC pins. Once an OVP has ime duration until the CC FETs at be removed for CC FETs to back on                                 |      | 0.6  |     | ms   |

| tovp_recove<br>ry_cc_1_db    | occurred, the minimum t                      | ne CC pins. Once an OVP has<br>ime duration until the CC FETs<br>ead battery resistors turn off.<br>for CC FETs to turn back on |      | 5    |     | ms   |

| tovp_recove<br>ry_sbu_1      | occurred, the minimun                        | e SBU pins. Once an OVP has<br>n time duration until the SBU<br>/P must be removed for SBU<br>turn back on                      |      | 0.5  |     | ms   |

| tovp_recove<br>ry_cc_2       | Removal until CC FET                         | e CC pins. Time from OVP s turn back on, if device has OVP > 0.6 ms                                                             |      | 0.2  |     | ms   |

| tovp_recove<br>ry_cc_2_db    | Removal until CC FETs                        | the CC pins. Time from OVP<br>turn back on and dead battery<br>ce has been in OVP > 0.6 ms                                      |      | 5    |     | ms   |

| SYMBOL                   | PARAMETER                                                                                                                      | MIN | TYP. | MAX | UNIT |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>OVP_RECOVE</sub>  | OVP recovery time on the SBU pins. Time from OVP<br>Removal until SBU FETs turn back on, if device has<br>been in OVP > 0.6 ms |     | 0.1  |     | ms   |

| t <sub>OVP_FLT_ASS</sub> | Time from OVP asserted to FLT assertion                                                                                        |     | 20   |     | μs   |

| tovp_flt_dea<br>ssertion | Time from CC FET turn on after an OVP to $\overline{\text{FLT}}$ Deassertion                                                   |     | 5    |     | ms   |

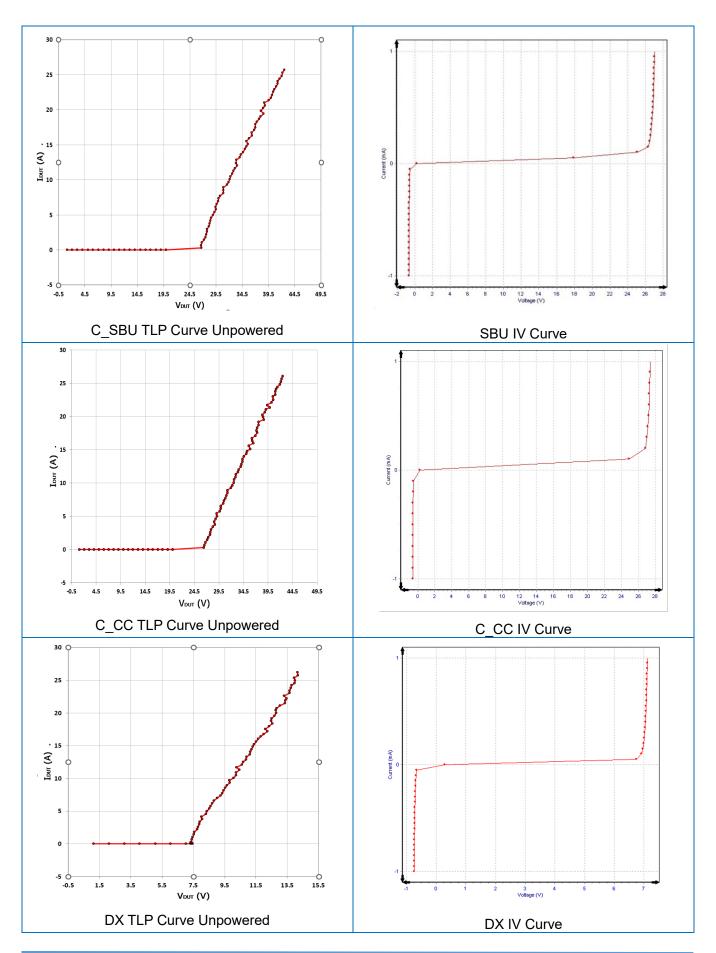

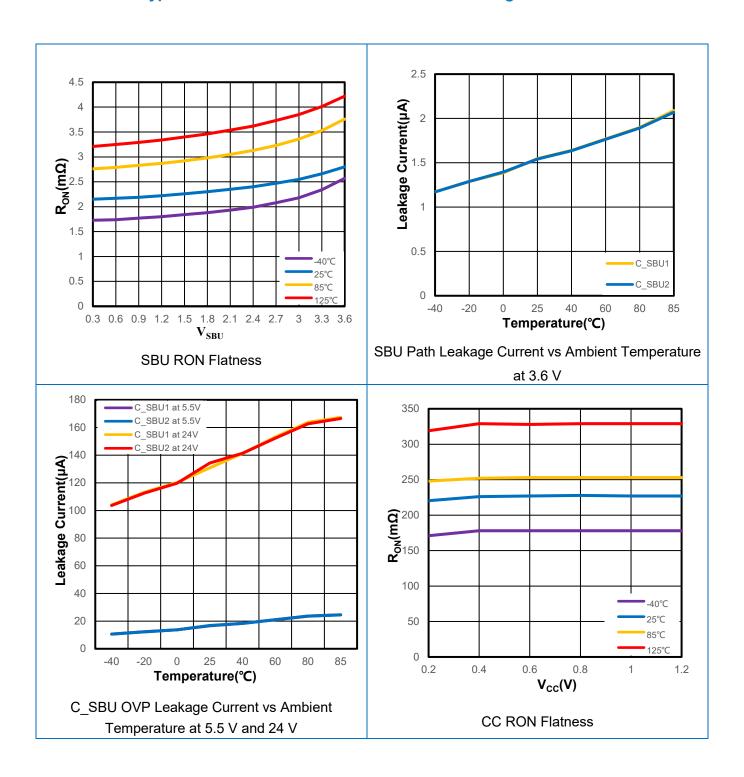

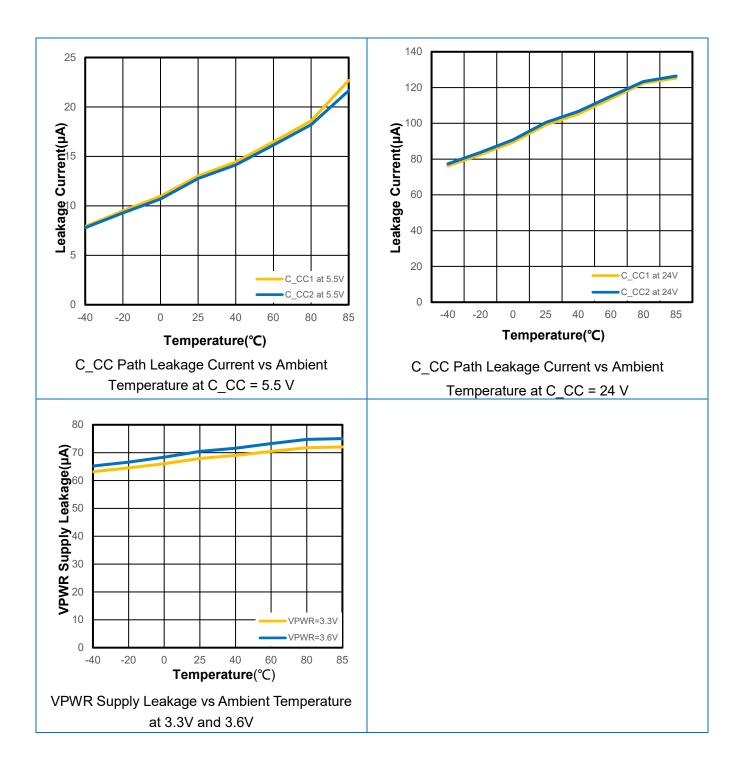

## 12. Typical Performance Characteristics

#### 13. Function Description

#### 13.1 Overview

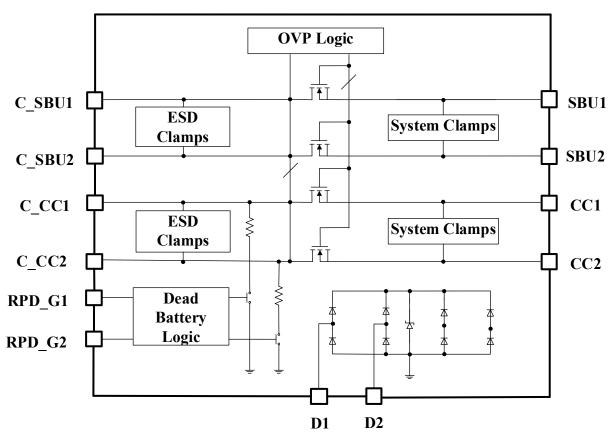

The WP5602 is a USB Type-C port protection chip that integrates four channels of 20-V Short-to-VBUS overvoltage protection for the CC1, CC2, SBU1, and SBU2 pins and six channels of IEC61000-4-2 ESD protection for the CC1, CC2, SBU1, SBU2, DP, DM pins of the USB Type-C connector.

#### 13.2 Block Diagram

#### 13.3 Feature Description

# 13.3.1 4-Channels of Short-to-VBUS Overvoltage Protection (CC1, CC2, SBU1, SBU2 Pins): 24-V<sub>DC</sub> Tolerant

The WP5602 provides 4-channels of Short-to-VBUS Overvoltage Protection for the CC1, CC2, SBU1, and SBU2 pins of the USB Type-C connector. The WP5602 is able to handle 24-VDC on its C\_CC1, C\_CC2, C\_SBU1, and C\_SBU2 pins. This is necessary because according to the USB PD specification, with VBUS set for 20-V operation, the VBUS voltage is allowed to legally swing up to 21 V, and 21.5 V on voltage transitions from a different USB PD VBUS voltage.

#### 13.3.2 6-Channels of IEC 61000-4-2 ESD Protection (CC1, CC2, SBU1, SBU2, DP, DM Pins)

The WP5602 integrates 6-Channels of IEC 61000-4-2 system level ESD protection for the CC1, CC2, SBU1, SBU2, DP, DM pins.

USB Type-C ports on end-products need system level IEC ESD protection in order to provide adequate protection for the ESD events that the connector can be exposed to from end users.

#### 13.3.3 Thermal Shutdown

Thermal shutdown protects the part from internally or externally generated excessive temperatures. During an overtemperature condition the switch is turned off. The switch automatically turns on again if the temperature of the die drops below the threshold temperature.

#### 13.3.4 Dead-battery Mode

The WP5602 integrates high voltage dead battery RD pull-down resistors to allow dead battery charging simultaneously with high-voltage OVP protection. If dead battery support is required, short the RPD\_G1 pin to the C\_CC1 pin, and short the RPD\_G2 pin to the C\_CC2 pin. This connects the dead battery resistors to the connector CC pins.

#### 14. Layout

For best performance, place the bypass capacitors as close as possible to the VPWR pin, and ESD protection capacitor as close as possible to the V<sub>BIAS</sub> pin. The USB2.0 and SBU lines must be routed as straight as possible and any sharp bends must be minimized.

#### 14.1 Layout Example

#### 15. Evaluation Modules

Evaluation Modules (EVMs) are available to help evaluate initial circuit performance. We have evaluation modules for different packages, you can contact us by phone or address at the end to get the evaluation module or schematic.

The module names are listed in the table below.

| NAME   | PACKAGE   | EVALUATION MODULE         |

|--------|-----------|---------------------------|

| WP5602 | QFN20 3*3 | TYPEC EVM V1.0 QFN3030-20 |

#### 16. Naming Conventions

#### WP AB CC-DDD E

WP: WAYON Protection IC;

A: Product Category –5: Type C Protection;

**B:** Number of Protection Channels –6: 6 Channels;

**CC:** Serial Number:

DDD: Package - Q3G: WQFN3\*3-20L;

E: R-Reel & T-tube;

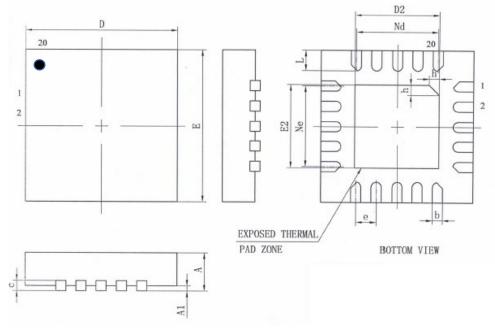

## 17. Package Information

#### QFN20 3\*3

| SYMBOL  | DIMENSIONS IN MILLIMETERS |      |      |  |

|---------|---------------------------|------|------|--|

|         | MIN                       | NOM  | MAX  |  |

| Α       | 0.7                       | 0.75 | 0.8  |  |

| A1      | -                         | 0.02 | 0.05 |  |

| b       | 0.15                      | 0.20 | 0.25 |  |

| С       | 0.18                      | 0.20 | 0.25 |  |

| D       | 2.90                      | 3.00 | 3.10 |  |

| D2      | 1.55                      | 1.65 | 1.75 |  |

| е       | 0.40BSC                   |      |      |  |

| Ne      | 1.60 BSC                  |      |      |  |

| ND      | 1.60 BSC                  |      |      |  |

| E       | 2.90                      | 3.00 | 3.10 |  |

| E2      | 1.55                      | 1.65 | 1.75 |  |

| L       | 0.35                      | 0.40 | 0.45 |  |

| h       | 0.20                      | 0.25 | 0.30 |  |

| L/F MIL | 75*75                     |      |      |  |

## 18. Ordering Information

| PART NUMBER | PACKAGE    | PACKING QUANTITY | MARKING*    |

|-------------|------------|------------------|-------------|

| WP5602-Q3GR | QFN3*3-20L | 3k/Reel          | WP5602 XXXX |

<sup>\*</sup> XXXX is variable.

#### **STATEMENTS**

WAY-ON provides data sheets based on the actual performance of the device, and users should verify actual device performance in their specific applications. The device characteristics and parameters in this data sheet can and do vary from application to application, and actual device performance may change over time. This information is intended for developers designing with WAY-ON products. Users are responsible for selecting the appropriate WAY-ON product for their application and for designing and verifying the application to ensure that your application meets the appropriate standards or other requirements, and users are responsible for all consequences. Specifications are subject to change without notice.

#### **Contact Information**

No.1001, Shiwan(7) Road, Pudong District, Shanghai, P.R.China.201202 Tel: 86-21-68960674 Fax: 86-21-50757680 Email: market@way-on.com

WAYON website: http://www.way-on.com

For additional information, please contact your local Sales Representative.

**ⅢfY IN** ® is registered trademark of Wayon Corporation.

Specifications are subject to change without notice.

The device characteristics and parameters in this data sheet can and do vary in different applications and actual device performance may vary over time.

Users should verify actual device performance in their specific applications.