# Zbit 128GB eMMC5.1 Datasheet ZBEM128G03RIF1

Rev 1.0

### Zbit Proprietary and Confidential

This specification is confidential and is subject to any Zbit handbooks or terms of use provided or made available to the customers. This specification is subject to change or being updated without notice. The customer assumes sale and exclusive responsibility for compliance with safety, environmental, export, trade and other applicable laws and regulations with respect to this specification.

## Overview

#### eMMC 5.1 specification compatibility

- Compatible to eMMC 4.41/4.51/5.0

#### Bus mode

- Data bus width: 1 bit (default), 4 bits, 8 bits

- Data transfer rate: up to 310MB/s (HS400)

- Timing mode: SDR/DDR/HS200/HS400

- I/F boot frequency: 0 ~ 52 MHz

- I/F clock frequency: 0 ~ 200 MHz

#### Operating voltage range

- VCC: 2.7 ~ 3.6V

- VCCQ: 1.7 ~ 1.95V or 2.7 ~ 3.6V

#### Temperature

- Operating temperature: -25 ~ 85°C

- Storage temperature: -45 ~ 85°C

#### Support feature

- RPMB Boot partition

- Write protection

- Erase, discard, trim, sanitize

- HPI

- Background operations

- Device health report

- Field firmware update (FFU)

- Sleep / awake

- Packed command

- Support Hardware ECC engine

- Support auto power save mode

- Preventing from sudden-power-off

# **Revision History**

| Rev  | Date      | History |

|------|-----------|---------|

| V1.0 | 2024/2/28 | Initial |

|      |           |         |

|      |           |         |

|      |           |         |

#### Zbit eMMC5.1 Datasheet

## Contents

| Revision History   3     1. Introduction   5     1.1 General Description   5     1.2 Dart Number   5     1.3 Ordering Information   5     2. Park Asignments   6     2.2 Signal Definition   6     2.3 Package Configuration   6     2.3 Package Dimension   8     3.0 Performance   9     3.1 Performance   9     3.2 Power Consumption   9     3.2 Power Consumption   9     3.2 Power Consumption   9     3.2 Step State   10     3.3 Terriformatice   10     3.3.3 Terriformatice   11     3.4 Partition Management   11     3.4 2 Partition Management   11     3.4 2 Partition Management   12     4.1 Penture List   12     4.2 Partition Management   12     4.3 Configuration   15     4.3.1 Boot Operation   15     4.3.2 Boot Operation   16     4.4 TWiteset operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16                                                              | Ove  | rview                        | 2  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|----|

| 1.1 General Description   5     1.2 Part Number   5     1.3 Ordering Information   5     2. Package Configuration   6     2.1 Fin Assignments   6     2.2 Signal Definition   6     2.3 Package Dimension   8     3. Product Specification   9     3.1 Performance   9     3.2 Power Consumption   9     3.2.1 Active State   10     3.2.2 Standby State   10     3.3 Temprature   10     3.4 Textfrom Size   11     3.4 Partition Management   11     3.4.1 Factory Configuration   11     3.4.1 Partition Management   12     4.1 Architecture and Application   12     4.1 Architecture and Application   15     4.3.2 Derition Management   16     4.4.5 lect Peration   15     4.3.2 Partition Management   16     4.4.1 WW Reset Operation   15     4.3.2 Partition Management   16     4.4.5 lectvic Health Report   16     4.4.5 lectvic Health Report   16     4.4.1 WW Reset Operation   15                           | Rev  | ision History                | 3  |

| 1.2 Part Number   5     1.3 Ordering Information   5     2. Package Configuration   6     2.1 Pin Assignments   6     2.2 Signal Definition   6     2.3 Package Dimension   8     9   3.1 Performance   9     3.1 Performance   9     3.2 Power Consumption   9     3.2 I Active State   90     3.2.2 Standby State   10     3.3 Temprature   10     3.4 Partition Size   11     3.4 Partition Size   11     3.4.1 Factory Configuration   11     3.4.1 Pactory Configuration   12     4.1 Architecture and Application   12     4.2 Fartition Management   15     4.3.1 Boot Operation   15     4.3.1 Boot Operation   15     4.3.1 Boot Operation   16     4.4 HW Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   18     4.7 Thermal Spec   20     4.8 AV Dever Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Satitize                                                       | 1.   | Intrduction                  | 5  |

| 1.2 Part Number   5     1.3 Ordering Information   5     2. Package Configuration   6     2.1 Pin Assignments   6     2.2 Signal Definition   6     2.3 Package Dimension   8     9   3.1 Performance   9     3.1 Performance   9     3.2 Power Consumption   9     3.2 I Active State   90     3.2.2 Standby State   10     3.3 Temprature   10     3.4 Partition Size   11     3.4 Partition Size   11     3.4.1 Factory Configuration   11     3.4.1 Pactory Configuration   12     4.1 Architecture and Application   12     4.2 Fartition Management   15     4.3.1 Boot Operation   15     4.3.1 Boot Operation   15     4.3.1 Boot Operation   16     4.4 HW Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   18     4.7 Thermal Spec   20     4.8 AV Dever Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Satitize                                                       |      | 1.1 General Description      | 5  |

| 1.3 Ordering Information   5     2. Package Configuration   6     2.1 Pin Assignments   6     2.2 Signal Definition   6     2.3 Package Dimension   8     3. Product Specification   9     3.1 Performance   9     3.2 Power Consumption   9     3.2 Power Consumption   9     3.2 Power Consumption   9     3.2.2 Standby State   10     3.2.3 Steep State   10     3.3 Temprature   10     3.4 Partition Nanagement   11     3.4.1 Factory Configuration   11     3.4.1 Pactory Configuration   12     4.1 Architecture and Application   12     4.2 Partition Management   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 HW Reset Operation   15     4.3.2 Derition Management   16     4.4 FPU Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FPU)   16     4.6 Field Firmware Update (FPU)   16 <                     |      | 1                            |    |

| 2. Package Configuration   6     2.1 Pin Assignments   6     2.2 Signal Definition   6     2.3 Package Dimension   8     Product Specification   9     3.1 Performance   9     3.2 Power Consumption   9     3.2 Power Consumption   9     3.2 Lactive State   9     3.2.1 Active State   9     3.2.2 Standby State   10     3.3 Temprature   11     3.4 Partition Size   10     3.3 Temprature   11     3.4 Partition Size   11     3.4.1 Pactory Configuration   12     4.1 Architecture and Application   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3.2 Partition Management   15     4.3.2 Partition Management   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.6.2 EXT_CSD Register for FFU   16     4.6.1 EFU Flow   16     4.6.2 EXT_CSD Register for FFU   16     4.7 Thermar                                          |      |                              |    |

| 2.1 Pin Assignments.   6     2.2 Signal Definition   6     2.3 Package Dimension   8     3.1 Performance   9     3.1 Performance   9     3.1 Performance   9     3.2 Power Consumption   9     3.2.1 Netromance   9     3.2.2 Standby State   10     3.2.3 Sleep State   10     3.3.3 Temprature   11     3.4 Partition Size   11     3.4.2 Partition Management   11     3.4.1 Pactory Configuration   12     4.1 Architecture and Application   12     4.3 Command Operation   12     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FPU Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Steep (CMD5)   21     4.1 Sequer Erse/Trim   21     4.1 Sequer Erse/Trim   22     5.1 OCR Register <td< td=""><td>2.</td><td></td><td></td></td<>          | 2.   |                              |    |

| 2.2 Signal Definition   6     2.3 Package Dimension   8     3. Product Specification   9     3.1 Performance   9     3.2 Power Consumption   9     3.2.1 Active State   9     3.2.2 Standby State   10     3.3 Temprature   10     3.4 Partition Size   11     3.4.1 Factory Configuration   11     3.4.2 Partition Management   11     3.4.1 Factory Configuration   12     4.1 Architecture and Application   12     4.1 Architecture and Application   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 HW Reset Operation   16     4.5 Device Health Report   16     4.6 EXT_CSD Register for FFU   16     4.6.1 FFU Plow,   16     4.6.1 FFU Plow,   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec.   21     5.1 OCR Register   22     5.2 CDR Register   22     5.3 CSD Register   22     5.4 SDR R                                          |      |                              |    |

| 2.3 Package Dimension   8     3. Product Specification   9     3.1 Performance   9     3.2 Power Consumption   9     3.2.1 Active State   9     3.2.2 Standby State   10     3.3 Temprature   10     3.3.3 Temprature   10     3.4 Partition Size   11     3.4 Partition Management   11     3.4.1 Factory Configuration   11     3.4.2 Partition Management   12     4.1 Architecture and Application   12     4.3 Command Operation   12     4.3 Command Operation   15     4.3 I Boot Operation   15     4.3 L Boot Operation   16     4.4 HW Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6 Field Pirmware Update (FFU)   16     4.6.1 FFU Flow.   16     4.7 Thermal Spec   20     2.9 Sin CDR Register for FFU   18     4.7 Thermal Spec   21     4.8 Auto Power Save Mode.   21     4.9 Sleep (CMD5).   21     4.10 Se                                          |      |                              |    |

| 3. Product Specification   9     3.1 Performance   9     3.2 Power Consumption   9     3.2.1 Active State   9     3.2.2 Standby State   10     3.2.3 Sleep State   10     3.2.3 Steep State   10     3.3 Temprature   11     3.4 Partition Size   11     3.4.1 Factory Configuration   11     3.4.2 Partition Management   11     4.4 Pontcional Description   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3 Command Operation   15     4.3.2 Partition Management   16     4.4 HW Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6 I FFU Flow   16     4.6 Z EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.11 Secure Erase/Trim   21     5.1 OCR Register   22     5.2 CDR Register   23     5.4 SDR Register   23     5.5 RCA Register <td></td> <td></td> <td></td>                |      |                              |    |

| 3.1 Performance   9     3.2 Power Consumption   9     3.2.1 Active State   9     3.2.2 Standby State   10     3.2.3 Steep State   10     3.3 Temprature   11     3.4 Partition Size   11     3.4 Partition Management   11     3.4.2 Partition Management   11     4.1 Architecture and Application   12     4.1 Architecture and Application   12     4.3 Command Operation   15     4.3.3 Boot Operation   15     4.3.3 Doot Operation   15     4.3.3 Doot Operation   15     4.3.2 Partition Management   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FUE Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.10 Sanitize   22     5.1 OCR Register   22     5.2 CID Register   23     5.4 Extended CSD Register                                                | 3    |                              |    |

| 3.2 Power Consumption   9     3.2.1 Active State   9     3.2.2 Standby State   10     3.2.3 Sleep State   10     3.3 Temprature   11     3.4 Partition Size   11     3.4.1 Factory Configuration   11     3.4.1 Partition Management   11     3.4.1 Partition Management   11     4.1 Architecture and Application   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3.1 Boot Operation   15     4.3.2 Dordperation   15     4.3.3 Boot Operation   15     4.3.4 Doot Operation   16     4.4 HW Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.6.1 FFU Flow   16     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMDS)   21     4.10 Sanitze   21     4.11 Secure Erase/Trim   21     5. Register   22     5. J CCR Register   22<                                                       | 5.   | 1                            |    |

| 3.2.1 Active State   9     3.2.2 Standby State   10     3.3 Temprature   10     3.4 Partition Size   11     3.4 Partition Size   11     3.4.1 Factory Configuration   11     3.4.2 Partition Management   11     3.4.2 Partition Management   11     4.1 Architecture and Application   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.5.2 Partition Management   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.6.1 FFU Flow   16     4.6.1 FFU Flow   16     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   22     5.1 CCR Register   22     5.2 CID Register   22     5.3 CSD Register   22     5.4 DCR Register   23     5.5 RCA Register   34 <td></td> <td></td> <td></td>                            |      |                              |    |

| 3.2.2 Standby State   10     3.2.3 Steep State   10     3.3 Temprature   11     3.4 Partition Size   11     3.4 Partition Size   11     3.4 Partition Management   11     3.4.1 Factory Configuration   11     3.4.2 Partition Management   11     4.1 Architecture and Application   12     4.1 Architecture and Application   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 H/W Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Scatter Erase/Trim   21     5. Register   22     5.1 CCR Register   22     5.2 CID Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   24     5.4 E                                          |      |                              |    |

| 3.2.3 Sleep Štate   10     3.3 Temprature   11     3.4 Partition Size   11     3.4.1 Factory Configuration   11     3.4.2 Partition Management   11     4.1 Architecture and Application   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 H/W Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.10 Sanitize   21     4.11 Scure Erase/Trim   21     5.1 OCR Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   23     5.5 SR CA Register   34     6.5 Electrical Characteristics   34     6.4 Bus Signal Line Load   34                                       |      |                              |    |

| 3.3 Temprature.   11     3.4 Partition Size   11     3.4.1 Factory Configuration   11     3.4.2 Partition Management   11     4. Functional Description   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4.4 H/W Reset Operation   16     4.5 Evice Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5. 1 OCR Register   22     5. 2 CID Register   22     5. 3 CSR Register   23     5.4 Extended CSD Register   23     5.5 S RCA Register   23     5.4 Extended CSD Register   24     5.5 S RCA Register   34     6. Electrical Characteristics   34                                        |      |                              |    |

| 3.4 Partition Size   11     3.4.1 Factory Configuration   11     3.4.2 Partition Management   11     4. Functional Description   12     4.1 Architecture and Application   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 W Reset Operation   16     4.5 Device Health Report   16     4.6.1 FFU Flow   16     4.6.1 FFU Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5.1 OCR Register   22     5.2 CID Register   23     5.4 Extended CSD Register   23     5.4 Extended CSD Register   34     6.5 Bus Signal Line Load   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34 <td< td=""><td></td><td></td><td></td></td<> |      |                              |    |

| 3.4.1 Factory Configuration   11     3.4.2 Partition Management   11     4.1 Architecture and Application   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 HW Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.10 Sanitize   21     4.10 Sanitize   21     4.10 Sanitize   21     5.1 OCR Register   22     5.2 CDR Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   23     5.4 Extended CSD Register   24     5.5 SRCA Register   34     6. Electrical Characteristics   34     6. Electric                                          |      |                              |    |

| 3.4.2 Partition Management.   11     4. Functional Description   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3 Command Operation   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 H/W Reset Operation   16     4.4 H/W Reset Operation   16     4.5 Device Health Report   16     4.6.1 FFU Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.10 Sanitize   22     5.1 OCR Register   22     5.2 CD Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   24     5.5 RCA Register   34     6.6 Electrical Characteristics   34     6.7 Designal Line Load   34     6.8 Signal Line Load   34     6.9 Signal Line Load   34     6.7 Design Guide <td></td> <td></td> <td></td>                |      |                              |    |

| 4. Functional Description   12     4.1 Architecture and Application   12     4.2 Feature List   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 H/W Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5. Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   22     5.4 Extended CSD Register   23     5.4 Extended CSD Register   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Line Load   34     6.4 Bus Timing Specification   35     6.4 Bus Timing Specification   35 <t< td=""><td></td><td></td><td></td></t<>  |      |                              |    |

| 4.1 Architecture and Application   12     4.2 Feature List   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 H/W Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.10 Sanitize   21     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   22     5.4 Extended CSD Register   23     5.4 Extended CSD Register   24     5.5 RCA Register   23     5.4 Extended CSD Register   34     6.6 Electrical Characteristics   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Line Load   34     6.4 Bus Timing Specification   36     6.                                          | 4 E  |                              |    |

| 4.2 Feature List   12     4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management   16     4.4 H/W Reset Operation   16     4.4 H/W Reset Operation   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   22     5.4 Extended CSD Register   23     5.4 Extended CSD Register   24     5.5 RCA Register   34     6.6 DSR Register   34     6.6 DSR Register   34     6.7 Dyply Voltage   34     6.3 Bus Signal Line Load   34     6.3 Bus Signal Line Load   34     6.4 Bus Timing Specification   36     7.1 Connect Guide                                                   | 4. Г |                              |    |

| 4.3 Command Operation   15     4.3.1 Boot Operation   15     4.3.2 Partition Management.   16     4.4.1W Reset Operation   16     4.4.1W Reset Operation   16     4.5 Device Health Report.   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow.   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode.   21     4.9 Sleep (CMD5)   21     4.10 Sanitize.   21     4.11 Secure Erase/Trim   21     5. Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   22     5.5 RCA Register   34     5.6 DSR Register   34     6.6 Electrical Characteristics   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Levels   35     6.4 Bus Timing Specification   36     6.4 Bus Timing Specification   36     7.1 Connect G                                          |      |                              |    |

| 4.3.1 Boot Operation   15     4.3.2 Partition Management.   16     4.4 H/W Reset Operation   16     4.4 H/W Reset Operation   16     4.5 Device Health Report.   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5. Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   22     5.4 Extended CSD Register   23     5.4 Extended CSD Register   24     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Levels   35     6.4 Bus Timing Specification   36     7.1 Connect Guide   37                                                                                                                                                                |      |                              |    |

| 4.3.2 Partition Management.   16     4.4 H/W Reset Operation   16     4.5 Device Health Report   16     4.5 Device Health Report   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5.1 OCR Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   22     5.4 Extended CSD Register   23     5.4 Extended CSD Register   24     6.4 Electrical Characteristics   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Levels   35     6.4 Bus Timing Specification   36     7.1 Connect Guide   37                                                                                                                                                 |      |                              |    |

| 4.4 H/W Reset Operation   16     4.5 Device Health Report.   16     4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow.   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode.   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5.1 OCR Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   23     5.5 RCA Register   34     6.6 DSR Register   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Levels   35     6.4 Bus Timing Specification   36     7.1 Connect Guide   37                                                                                                                                                                                                                                            |      |                              |    |

| 4.5 Device Health Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                              |    |

| 4.6 Field Firmware Update (FFU)   16     4.6.1 FFU Flow.   16     4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode.   21     4.9 Sleep (CMD5).   21     4.10 Sanitize.   21     4.10 Sanitize.   21     4.11 Secure Erase/Trim   21     5. Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   22     5.5 RCA Register   23     5.4 Extended CSD Register   34     5.6 DSR Register   34     6.6 Ilsupply Voltage   34     6.1 Supply Voltage   34     6.3 Bus Signal Line Load   34     6.4 Bus Timing Specification   36     7.1 Connect Guide   37                                                                                                                                                                                                                                                                                            |      |                              |    |

| 4.6.1 FFU Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                              |    |

| 4.6.2 EXT_CSD Register for FFU   18     4.7 Thermal Spec   20     4.8 Auto Power Save Mode.   21     4.9 Sleep (CMD5)   21     4.10 Sanitize.   21     4.11 Secure Erase/Trim   21     5. Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   23     5.5 RCA Register   34     5.6 DSR Register   34     6. Electrical Characteristics   34     6.1 Supply Voltage   34     6.3 Bus Signal Line Load   34     6.4 Bus Timing Specification   36     7. Design Guide   37     7.1 Connect Guide   37                                                                                                                                                                                                                                                                                                                                                     |      |                              |    |

| 4.7 Thermal Spec   20     4.8 Auto Power Save Mode   21     4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5. Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   25     5.5 RCA Register   34     6. Electrical Characteristics   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Levels   35     6.4 Bus Timing Specification   36     7. Design Guide   37     7.1 Connect Guide   37                                                                                                                                                                                                                                                                                                                                                                                          |      |                              |    |

| 4.8 Auto Power Save Mode.   21     4.9 Sleep (CMD5)   21     4.10 Sanitize.   21     4.11 Secure Erase/Trim   21     5. Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   25     5.5 RCA Register   25     5.6 DSR Register   34     6.6 Electrical Characteristics   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Line Load   35     6.4 Bus Timing Specification   36     7. Design Guide   37     7.1 Connect Guide   37                                                                                                                                                                                                                                                                                                                                                                                    |      |                              |    |

| 4.9 Sleep (CMD5)   21     4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5. Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   25     5.5 RCA Register   25     5.6 DSR Register   34     5.6 DSR Register   34     6. Electrical Characteristics   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Levels   35     6.4 Bus Timing Specification   36     7. Design Guide   37     7.1 Connect Guide   37                                                                                                                                                                                                                                                                                                                                                                                                  |      |                              |    |

| 4.10 Sanitize   21     4.11 Secure Erase/Trim   21     5. Register   22     5.1 OCR Register   22     5.2 CID Register   22     5.3 CSD Register   23     5.4 Extended CSD Register   25     5.5 RCA Register   25     5.6 DSR Register   34     5.6 DSR Register   34     6. Electrical Characteristics   34     6.1 Supply Voltage   34     6.2 Bus Signal Line Load   34     6.3 Bus Signal Levels   35     6.4 Bus Timing Specification   36     7. Design Guide   37     7.1 Connect Guide   37                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                              |    |

| 4.11 Secure Erase/Trim215. Register225.1 OCR Register225.2 CID Register225.3 CSD Register235.4 Extended CSD Register255.5 RCA Register345.6 DSR Register346. Electrical Characteristics346.1 Supply Voltage346.2 Bus Signal Line Load346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                              |    |

| 5. Register225.1 OCR Register225.2 CID Register225.3 CSD Register235.4 Extended CSD Register255.5 RCA Register345.6 DSR Register346. Electrical Characteristics346.1 Supply Voltage346.2 Bus Signal Line Load346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                              |    |

| 5.1 OCR Register225.2 CID Register225.3 CSD Register235.4 Extended CSD Register255.5 RCA Register345.6 DSR Register346. Electrical Characteristics346.1 Supply Voltage346.2 Bus Signal Line Load346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                              |    |

| 5.2 CID Register225.3 CSD Register235.4 Extended CSD Register255.5 RCA Register345.6 DSR Register346. Electrical Characteristics346.1 Supply Voltage346.2 Bus Signal Line Load346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5. R |                              |    |

| 5.3 CSD Register235.4 Extended CSD Register255.5 RCA Register345.6 DSR Register346. Electrical Characteristics346.1 Supply Voltage346.2 Bus Signal Line Load.346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                              |    |

| 5.4 Extended CSD Register255.5 RCA Register345.6 DSR Register346. Electrical Characteristics346.1 Supply Voltage346.2 Bus Signal Line Load.346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                              |    |

| 5.5 RCA Register345.6 DSR Register346. Electrical Characteristics346.1 Supply Voltage346.2 Bus Signal Line Load346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                              |    |

| 5.6 DSR Register346. Electrical Characteristics346.1 Supply Voltage346.2 Bus Signal Line Load346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                              |    |

| 6. Electrical Characteristics346.1 Supply Voltage346.2 Bus Signal Line Load346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                              |    |

| 6.1 Supply Voltage346.2 Bus Signal Line Load346.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                              |    |

| 6.2 Bus Signal Line Load.346.3 Bus Signal Levels356.4 Bus Timing Specification.367. Design Guide.377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6. E |                              |    |

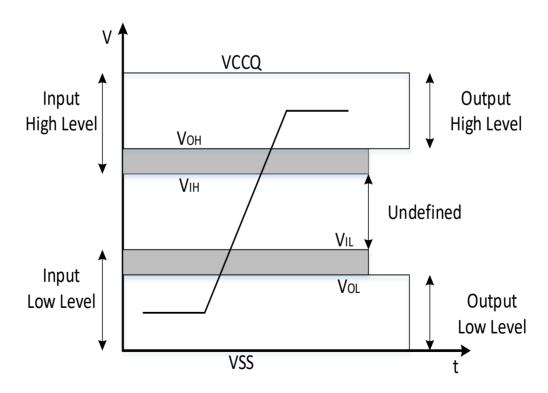

| 6.3 Bus Signal Levels356.4 Bus Timing Specification367. Design Guide377.1 Connect Guide37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 6.1 Supply Voltage           | 34 |

| 6.4 Bus Timing Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 6.2 Bus Signal Line Load     | 34 |

| 7. Design Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 6.3 Bus Signal Levels        | 35 |

| 7.1 Connect Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 6.4 Bus Timing Specification | 36 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7.   | Design Guide                 | 37 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 7.1 Connect Guide            | 37 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 7.2 Component Recommendation | 37 |

# 1. Intrduction

### **1.1 General Description**

Zbit eMMC device consists of NAND flash and a built-in MMC controller. This product is a high performance and quality embedded storage solution and compatible with JEDEC standard eMMC5.1 specification. Its strong ECC engine significantly improves error correction enabling longer device lifetime and an increased ability to handle higher raw bit error rate. The eMMC controller and software directly manage NAND flash, including ECC, wear-leveling, bad block management, garbage collection and performance optimization, and manage interface protocols. This architecture insulates any revision of NAND flash from the eMMC Host, makes the device easy to integrate and accelerates time-to-market.

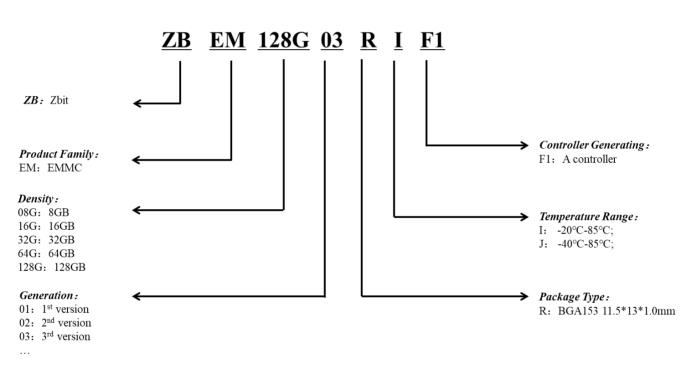

### 1.2 Part Number

### **1.3 Ordering Information**

Please contact Zbit regional sales for the latest product selection and available form factors.

| Table 1 Ordering Information |

|------------------------------|

|------------------------------|

| Part Number    | Density | Package Type | Package<br>Dimensions      | Shipping |

|----------------|---------|--------------|----------------------------|----------|

| ZBEM128G03RIF1 | 128GB   | BGA153       | 11.5*13*1.0mm <sup>3</sup> | Tray     |

# 2. Package Configuration

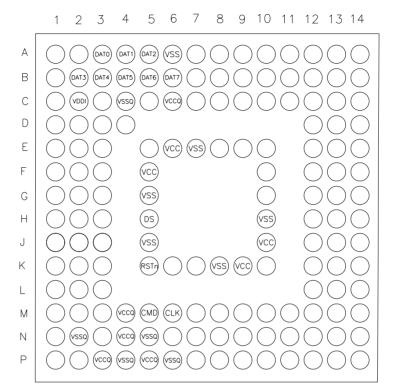

### 2.1 Pin Assignments

Figure 1. Ball Mapping

### 2.2 Signal Definition

| Signal | Туре | Description                                                                                                                                                                        |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAT0   | I/O  | Data I/O: These are bidirectional data signals. The DAT signals operate in push-pull                                                                                               |

| DAT1   | I/O  | mode. By default, after power-on or assertion of the RST_n signal, only DAT0 is used for data transfer. The MMC controller can configure a wider data bus for data transfer        |

| DAT2   | I/O  | either using DAT [3:0] (4-bit mode) or DAT [7:0] (8-bit mode). eMMC includes internal                                                                                              |

| DAT3   | I/O  | pull-up resistors for data lines DAT [7:1]. Immediately after entering the 4-bit mode, the device disconnects the internal pull-up resistors on the DAT [3:1] lines. Upon entering |

| DAT4   | I/O  | the 8-bit mode, the device disconnects the internal pull-ups on the DAT [7:1] lines.                                                                                               |

| Signal        | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAT5          | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DAT6          | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DAT7          | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CMD           | I/O  | Command: This signal is a bidirectional command channel used for command and response transfers. The CMD signal has two bus modes: open-drain mode and push-pull mode. Commands are sent from the MMC host to the device, and responses are sent from the device to the host.                                                                                                                                                                                                      |

| CLK           | Ι    | Clock: Each cycle of the clock directs a transfer on the command line and on the data line(s). The frequency can vary between the minimum and the maximum clock frequency.                                                                                                                                                                                                                                                                                                         |

| RST_n         | I    | Reset: The RST_n signal is used by the host for resetting the device, moving the device<br>to the pre-idle state. By default, the RST_n signal is temporarily disabled in the device.<br>The host must set EXT_CSD register byte 162, bits [1:0] to 0x1 to enable this<br>functionality before the host can use it.                                                                                                                                                                |

| DS            | 0    | Data strobe: Generated by the device and used for data output and CRC status response<br>output in HS400 mode. The frequency of this signal follows the frequency of CLK. For<br>data output, each cycle of this signal directs two bits transfer (2x) on the data, one bit for<br>the positive edge and the other bit for the negative edge. For CRC status response<br>output, the CRC status is latched on the positive edge only, and is "Don't Care" on the<br>negative edge. |

| VCC           | Р    | VCC: NAND interface I/O and NAND Flash power supply                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VCCQ          | Р    | VCCQ: eMMC controller core and eMMC I/F I/O power supply.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VSS           | Р    | VSS: NAND interface I/O and NAND Flash ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VSSQ          | Р    | VSSQ: eMMC controller core and eMMC I/F ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VDDI<br>Note: | -    | Internal voltage node.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### Note:

1) I/O = Bi-direction, I = Input, O = Output, P = Power/Analog

2) VSS and VSSQ are connected internally.

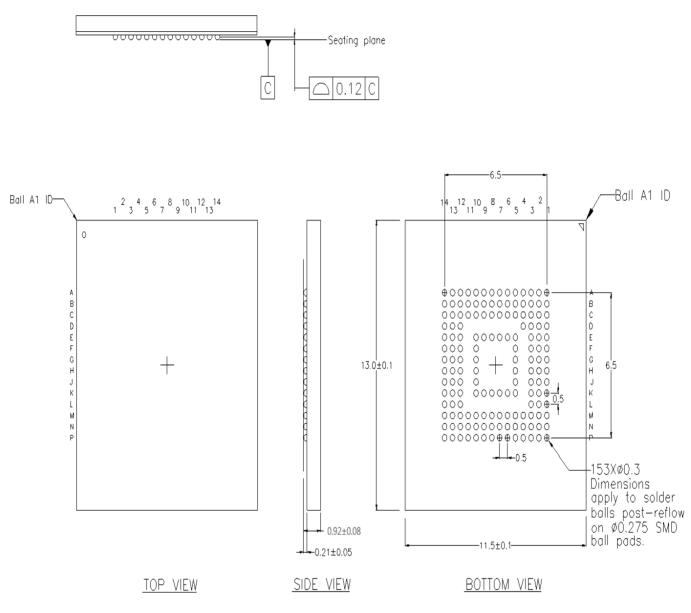

### 2.3 Package Dimension

Figure 2. Package Dimension of BGA153

# 3. Product Specification

### 3.1 Performance

| Mada    | I. to an | Sequential Speed (MB/s) |  |  |

|---------|----------|-------------------------|--|--|

| Mode    | Item     | 128GB                   |  |  |

| 115 400 | Write    | 251                     |  |  |

| HS400   | Read     | 310                     |  |  |

| HS200   | Write    | 101                     |  |  |

|         | Read     | 170                     |  |  |

| DDR52   | Write    | 80                      |  |  |

|         | Read     | 83                      |  |  |

Table 3. Performance value in initial stage.

Note:

1. Test condition: Under Zbit internal test board, 512KB data transfer, cache on, without OS overhead.

2. Device will exit initial stage and never return to the initial stage again, when the accumulated data size written into different LBAs is greater than the half of device capacity.

### **3.2 Power Consumption**

### 3.2.1 Active State

| Table 4. Power consumption in active | state |

|--------------------------------------|-------|

|--------------------------------------|-------|

| Mode   | Operation | Item             | Power Consumption (mA) |  |  |

|--------|-----------|------------------|------------------------|--|--|

| Wout   | operation | Ittin            | 128GB                  |  |  |

|        | Read      | I <sub>CC</sub>  | 117                    |  |  |

| HS400  | Read      | Iccq             | 65                     |  |  |

| 113400 | Write     | Icc              | 105                    |  |  |

|        |           | I <sub>CCQ</sub> | 49                     |  |  |

| HS200  | Read      | Icc              | 95                     |  |  |

| 115200 | Read      | I <sub>CCQ</sub> | 50                     |  |  |

#### Zbit eMMC5.1 Datasheet

|       | Write | I <sub>CC</sub>  | 85 |

|-------|-------|------------------|----|

|       | Wille | I <sub>CCQ</sub> | 45 |

| DDR52 | Read  | I <sub>CC</sub>  | 70 |

|       |       | Iccq             | 48 |

|       | Write | Icc              | 68 |

|       |       | Iccq             | 40 |

Note:

1. The measurement for max RMS current is the average RMS current consumption over a period of 100ms.

2. Device operation under 3.3V  $V_{CC}$  and 1.8V  $V_{CCQ}$ .

### 3.2.2 Standby State

| Table 5.  | Power  | consumption | in | standby state |

|-----------|--------|-------------|----|---------------|

| 1 uoie 5. | 100001 | consumption |    | Stundoy Stuto |

| Density | I <sub>CCQ</sub> | (uA) | I <sub>CC</sub> (uA) |      |

|---------|------------------|------|----------------------|------|

|         | 25°C (Typ.)      | 85°C | 25°C (Typ.)          | 85°C |

| 128GB   | 100              | 470  | 50                   |      |

Note:

1. The measurement for max RMS current is the average RMS current consumption over a period of 100ms.

2. In Standby Power mode, VCCQ & VCC power supply is switched on. No data transaction period before entering sleep status, no clock. VCCQ = 1.8V & VCC = 3.3V. Not 100% tested.

### 3.2.3 Sleep State

|  | Table 6. | Power | consumption | in | sleep | state |

|--|----------|-------|-------------|----|-------|-------|

|--|----------|-------|-------------|----|-------|-------|

| Density | I <sub>CCQ</sub> ( | I <sub>CC</sub> ( <b>u</b> A) |   |

|---------|--------------------|-------------------------------|---|

| Density | 25°C(Typ.)         | 85°C                          |   |

| 128GB   | 100                | 470                           | 0 |

#### Note:

1. The measurement for max RMS current is the average RMS current consumption over a period of 100ms.

2. In Sleep state, triggered by CMD5,  $V_{CC}$  power supply is switched off ( $V_{CCQ}$  on).  $V_{CCQ} = 1.8V \& V_{CC} = 0V$ . Not 100% tested.

3. In auto power saving mode, NAND power  $V_{CC}$  cannot be switched off. However, in sleep mode  $V_{CC}$  can be switched off. If NAND power  $V_{CC}$  is alive, it is same with that of the Standby state.

### 3.3 Temprature

| Symbol    | Min (°C) | Max (°C) |

|-----------|----------|----------|

| Operation | -25      | 85       |

| Storage   | -40      | 85       |

### 3.4 Partition Size

### **3.4.1 Factory Configuration**

The device initially consists of two Boot Partitions, RPMB Partition and User Data Area. Both Boot and RPMB area have fixed size of area and cannot be adjusted.

| Density | Boot Partition 1 | Boot Partition 2<br>(KB) | RPMB          | User Data Area |           |

|---------|------------------|--------------------------|---------------|----------------|-----------|

| Density | ( <b>KB</b> )    |                          | ( <b>KB</b> ) | Percent        | Size (MB) |

| 128GB   | 4096             | 4096                     | 4096          | 91%            | 119,280   |

Table 8. Partition Size

### 3.4.2 Partition Management

The User Data Area can be divided into four General Purpose Area Partitions and User Data Area partition with independent address spaces, starting from logical address 0x0000000. Each of the General Purpose Area Partitions and a section of User Data Area partition can be configured as enhanced partition. These partition management operations are one-time programmable.

The enhanced partitions are true SLC mode partition. When customer set some portion as enhanced partitions in User Data Area, these partitions occupy double (MLC)/triple (TLC) size of the original set-up size. If set 1MB for enhanced mode, total 2MB(MLC)/3MB(TLC) user data area is needed to generate 1MB enhanced area.

| Table 9. Max Enhanced Partition Size | Table 9. | Max | Enhanced | Partition | Size |

|--------------------------------------|----------|-----|----------|-----------|------|

|--------------------------------------|----------|-----|----------|-----------|------|

| Density | Max. Enhanced Partition Size |

|---------|------------------------------|

| 128GB   | 39,760 MB                    |

# 4. Functional Description

### Zbit eMMC5.1 Datasheet

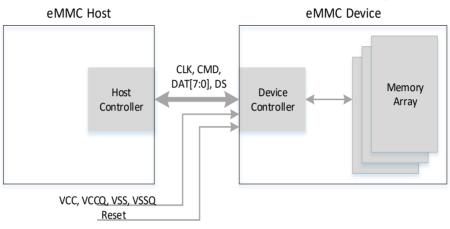

### 4.1 Architecture and Application

The eMMC device consists of a single chip eMMC controller and NAND flash memory. The controller interfaces with a host system allowing data to be written to and read from the NAND flash memory, and handles flash management, including logical to physical translation, bad block management, wear leveling and so on. The interface is only 12-bit line, can support 1-bit/4-bit/8-bit data bus flexibly. Therefore, eMMC host can integrate the eMMC easily, access it like a MMC card, and do not care about NAND flash management.

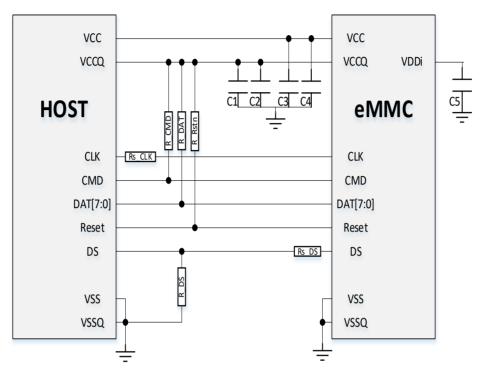

Figure 3. eMMC System Overview

### 4.2 Feature List

The table below lists which common features following JEDEC standards this device supports, and this section introduces several key features of them. For more detailed information about each feature, please refer to JESD84-B51 standard.

| Table 10. St | pported Fe | eature List |

|--------------|------------|-------------|

|--------------|------------|-------------|

| Feature              | Benefit                              | Support |

|----------------------|--------------------------------------|---------|

| Legacy 25/52MHz SDR  |                                      | Y       |

| 3.3V VCCQ            |                                      | Y       |

| 1.8V VCCQ            |                                      | Y       |

| 52MHz DDR            |                                      | Y       |

| Auto Power Save Mode |                                      | Y       |

| Background Operation | Better User Experience (low latency) | Y       |

| Feature                                       | Benefit                                                                       | Support |

|-----------------------------------------------|-------------------------------------------------------------------------------|---------|

| Boot Partition and Operation                  |                                                                               | Y       |

| Boot Partition Individual Write<br>Protection |                                                                               | Y       |

| <b>BKOPS</b> Control                          | Host control on BKOPs                                                         | Y       |

| Cache                                         | Better Sequential & Random Writes                                             | Y       |

| Cache Barrier                                 |                                                                               | Y       |

| Cache Flush Report                            |                                                                               | Y       |

| Command Queuing                               |                                                                               | Y       |

| Context Management                            | Performance and/or Reliability                                                | Y       |

| Configurable Drive Strength                   |                                                                               | Y       |

| Discard                                       | Improved Performance on Full Media                                            | Y       |

| Data Tag                                      | Performance and/or Reliability                                                | Y       |

| Data Reliability Definition                   | Static Data Protection                                                        | Y       |

| Dynamic Capacity                              |                                                                               | Y       |

| Device Health Report                          | Vital NAND info                                                               | Y       |

| E2MMC                                         |                                                                               | Ν       |

| Enhanced Strobe                               | Sync Data out, CRC Response and CMD response between Device and Host in HS400 | Y       |

| Enhanced Reliable Write                       |                                                                               | Y       |

| Extended Partition Attribute                  | Flexibility                                                                   | Y       |

| Extended Security Protocols                   |                                                                               | Ν       |

| Field Firmware Update                         |                                                                               | Y       |

| FW Configuration Register                     |                                                                               | Y       |

| Feature                                    | Benefit                               | Support |

|--------------------------------------------|---------------------------------------|---------|

| HPI(High Priority Interrupt)               | Control Long Reads/Writes             | Y       |

| HW Reset                                   | Robust System Design                  | Y       |

| HS200                                      | Speed                                 | Y       |

| HS400                                      | Speed                                 | Y       |

| Independent Boot Area Protection           |                                       | Y       |

| I/O Modification<br>(Overshoot/Undershoot) |                                       | Y       |

| Large Sector Size                          | Potential performance                 | Ν       |

| Partitioning & Protection                  | Flexibility                           | Y       |

| Power Off Notification                     | Faster Boot; Responsiveness           | Y       |

| Packed Command                             | Reduce Host Overhead                  | Y       |

| Production State Awareness                 | Different operation during production | Y       |

| Real Time Clock                            |                                       | Y       |

| Reliable Write                             |                                       | Y       |

| RPMB Throughput Improve                    | Faster RPMB write throughput          | Y       |

| RPMB                                       | Secure Folders                        | Y       |

| Sanitize                                   | True Wipe                             | Y       |

| Secure Erase                               | True Wipe                             | Y       |

| Secure TRIM                                | True Wipe                             | Y       |

| Secure Removal Type                        |                                       | Y       |

| Sleep Mode                                 |                                       | Y       |

| Sleep Notification                         |                                       | Y       |

#### Zbit eMMC5.1 Datasheet

| Feature                 | Benefit              | Support |

|-------------------------|----------------------|---------|

| Secure Write Protection | Secure Write Protect | Y       |

| Thermal Spec.           |                      | Y       |

| Trim                    |                      | Y       |

| VSF Signals             |                      | Y       |

| Write Reliability       |                      | Y       |

### 4.3 Command Operation

### 4.3.1 Boot Operation

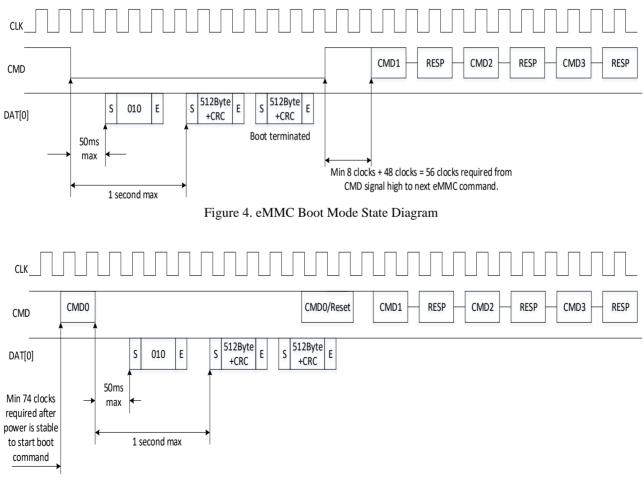

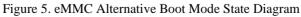

Device supports both boot mode and alternative boot mode. Device supports high speed timing and dual data rate during boot mode.

#### Zbit eMMC5.1 Datasheet

Table 11. Timing Parameter

|                         | 6       |

|-------------------------|---------|

| Timing Parameter        | Value   |

| (1) Boot ACK Time       | < 50 ms |

| (2) Boot Data Time      | < 1 s   |

| (3) Initialization Time | < 1 s   |

### 4.3.2 Partition Management

The device initially consists of two Boot partitions, RPMB partitions and user data area. The User Data Area can be divided into four General Purpose Area Partitions and User Data Area partition. Each of the General Purpose Area partitions and a section of User Data Area partition can be configured as enhanced partition. For more details, please refer to JESD84-B51 standard.

### 4.4 H/W Reset Operation

H/W reset operation may be used to reset the device, moving the device to a pre-idle state. For more information, refer to JESD84-B51 standard.

### 4.5 Device Health Report

Device supports Device Health Report feature which can provide an estimated indication about the device lifetime that is reflected by the averaged wear out of memory Type A and Type B. It can be queried by standard eMMC command for getting Extended CSD structure. Please refer to below and JEDEC Standards for details.

| Field                      | EXT_CSD Slice | Description                                                           |

|----------------------------|---------------|-----------------------------------------------------------------------|

| DEVICE_LIFE_TIME_EST_TYP_A | 268           | Lifetime estimation of Type A(SLC) area.                              |

| DEVICE_LIFE_TIME_EST_TYP_B | 269           | Lifetime estimation of Type B(MLC/TLC) area.                          |

| PRE_EOL_INFO               | 267           | Indication about device lifetime reflected by average reserved blocks |

| Table 12. Device Health Report |

|--------------------------------|

|--------------------------------|

The device health feature will provide a % of the wear of the device in 10% fragments.

### 4.6 Field Firmware Update (FFU)

### 4.6.1 FFU Flow

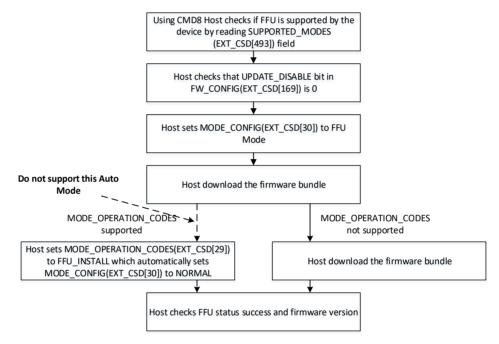

The feature of Field Firmware Update (FFU) is used to

•

#### Zbit eMMC5.1 Datasheet

update the device firmware with an open protocol to users. The host can download a new version of the firmware into the eMMC device by this mechanism and whole FFU process can happen without affecting any user/OS data.

- Field Firmware Update is protected from power interruption events. Any power loss interruption will not corrupt the firmware [device may initialize from next power for either the old or the new firmware).

- Any failure of Field Firmware Update will cause the previous version of firmware to be restored.

- Field Firmware Update supports all bus widths and clocks.

- The binary of Field Firmware Update is protected from invalid firmware Any invalid firmware will cause a Field Firmware Update failure rather than update the device with the wrong firmware.

- The older version of binary cannot be updated with Field Firmware Update To update the device with an older version of firmware, the VSC command, MP Flow, should be issued.